# Brought to You by

Like the book? Buy it!

## **Nonlinear Microwave and RF Circuits**

**Second Edition**

### **Nonlinear Microwave and RF Circuits**

### **Second Edition**

Stephen A. Maas

### Library of Congress Cataloging-in-Publication Data

Maas, Stephen A.

Nonlinear microwave and RF circuits / Stephen A. Maas.—2nd ed.

p. cm.

Rev. and updated ed. of: Nonlinear microwave circuits, 1988 and reprinted in 1997. Includes bibliographical references and index.

ISBN 1-58053-484-8 (alk. paper)

1. Microwave circuits. I. Maas, Stephen A. Nonlinear microwave circuits. II. Title.

TK7876.M284 2003 621.381'32—dc21

2002043664

### British Library Cataloguing in Publication Data

Maas, Stephen A.

Nonlinear microwave and RF circuits. — 2nd ed.— (Artech House microwave library)

1. Microwave circuits 2. Radio circuits 3. Electronic networks,

Nonlinear

I. Titles

621.3'8132

ISBN 1-58053-484-8

Cover design by Gary Ragaglia

© 2003 ARTECH HOUSE, INC. 685 Canton Street Norwood, MA 02062

All rights reserved. Printed and bound in the United States of America. No part of this book may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the publisher.

All terms mentioned in this book that are known to be trademarks or service marks have been appropriately capitalized. Artech House cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark.

International Standard Book Number: 1-58053-484-8 Library of Congress Catalog Card Number: 2002043664

## **Contents**

| Preface   |       |          |                                       | xix |

|-----------|-------|----------|---------------------------------------|-----|

| Chapter 1 | Intro | duction, | Fundamental Concepts, and Definitions | 1   |

|           | 1.1   | Linear   | ity and Nonlinearity                  | 1   |

|           | 1.2   | Freque   | ency Generation                       | 4   |

|           | 1.3   | Nonlin   | near Phenomena                        | 13  |

|           |       | 1.3.1    | Harmonic Generation                   | 13  |

|           |       | 1.3.2    | Intermodulation Distortion            | 14  |

|           |       | 1.3.3    | Saturation and Desensitization        | 14  |

|           |       | 1.3.4    | Cross Modulation                      | 15  |

|           |       | 1.3.5    | AM-to-PM Conversion                   | 15  |

|           |       | 1.3.6    | Spurious Responses                    | 16  |

|           |       | 1.3.7    | Adjacent Channel Interference         | 16  |

|           | 1.4   | Appro    | aches to Analysis                     | 17  |

|           |       | 1.4.1    | Load Pull                             | 17  |

|           |       | 1.4.2    | Large-Signal Scattering Parameters    | 18  |

|           |       | 1.4.3    | Time-Domain (Transient) Analysis      | 19  |

|           |       | 1.4.4    | Frequency-Domain Methods              | 19  |

|           |       | 1 4 5    | The Quasistatic Assumption            | 20  |

| N | On | linear | Mici | owave | and | RF | Circ | nits |

|---|----|--------|------|-------|-----|----|------|------|

|   |    |        |      |       |     |    |      |      |

viii

|           | 1.5   | Power           | and Gain Definitions                                            | 21         |

|-----------|-------|-----------------|-----------------------------------------------------------------|------------|

|           | 1.6   | Stabili         | ty                                                              | 26         |

|           | Refer | ence            |                                                                 | 27         |

| Chapter 2 | Solid | -State D        | evice Modeling for Quasistatic Analysis                         | 29         |

|           | 2.1   | Nonlin          | ear Device Models                                               | 29         |

|           | 2.2   |                 | ear Lumped Circuit Elements and<br>lled Sources                 | 31         |

|           |       | 2.2.1           | The Substitution Theorem                                        | 33         |

|           |       | 2.2.2           | Large-Signal Nonlinear Resistive Elements                       | 34         |

|           |       | 2.2.3           | Small-Signal Nonlinear Resistive Elements                       | 35         |

|           |       | 2.2.4           | Large-Signal Nonlinear Capacitance                              | 38         |

|           |       | 2.2.5           | Small-Signal Nonlinear Capacitance                              | 39         |

|           |       | 2.2.6           | Relationship Between $I/V$ , $Q/V$ and $G/V$ , $C/V$ Expansions | <b>4</b> ] |

|           |       | 2.2.7           | Multiply Controlled Nonlinear Capacitors                        | 43         |

|           |       | 2.2.8           | Nonlinear Inductance                                            | 47         |

|           | 2.3   | Numer<br>Models | ical and Human Requirements for Device                          | 48         |

|           |       | 2.3.1           | Continuous Derivatives in $I/V$ or $Q/V$ Expressions            | 48         |

|           |       | 2.3.2           | Accuracy of Derivatives                                         | 49         |

|           |       | 2.3.3           | Range of Expressions                                            | 49         |

|           |       | 2.3.4           | Transient-Analysis Models in Harmonic-Balance Analysis          | 5(         |

|           |       | 2.3.5           | Matrix Conditioning                                             | 5(         |

|           |       | 2.3.6           | Limiting the Range of Control Voltages                          | 51         |

|           |       | 2.3.7           | Use of Polynomials                                              | 52         |

|           |       | 2.3.8           | Loops of Control Voltages                                       | 53         |

|           |       | 2.3.9           | Default Parameters                                              | 53         |

| ix |

|----|

|    |

|     | 2.3.10  | Error Trapping                    | 54  |

|-----|---------|-----------------------------------|-----|

|     | 2.3.11  | Lucidity of Models and Parameters | 55  |

|     | 2.3.12  | Does Complexity Improve a Model?  | 55  |

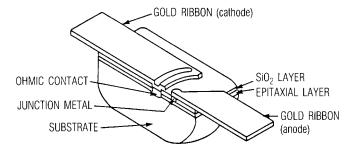

| 2.4 | Schottk | xy-Barrier and Junction Diodes    | 56  |

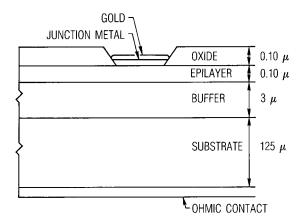

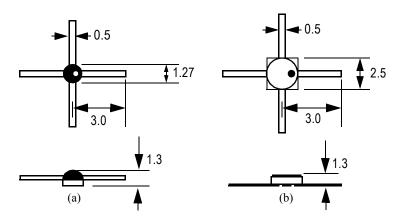

|     | 2.4.1   | Structure and Fabrication         | 57  |

|     | 2.4.2   | The Schottky-Barrier Diode Model  | 58  |

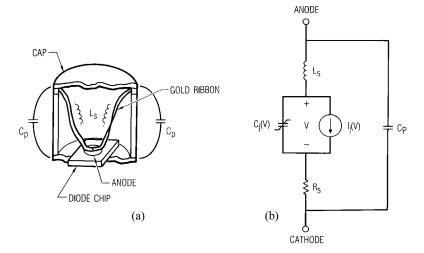

|     | 2.4.3   | Mixer Diodes                      | 65  |

|     | 2.4.4   | Schottky-Barrier Varactors        | 66  |

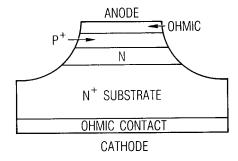

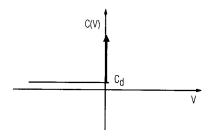

|     | 2.4.5   | $p^+n$ Junction Varactors         | 68  |

|     | 2.4.6   | Varactor Modeling                 | 70  |

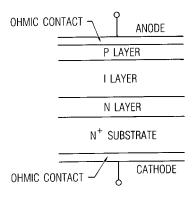

|     | 2.4.7   | Step-Recovery Diodes              | 71  |

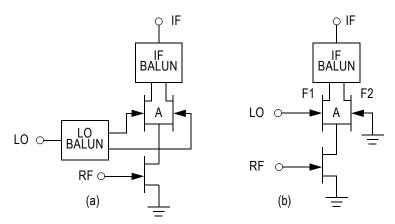

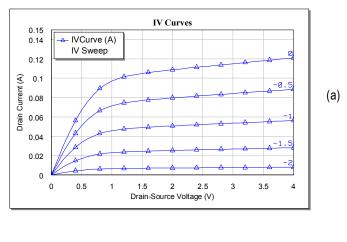

| 2.5 | FET D   | evices                            | 73  |

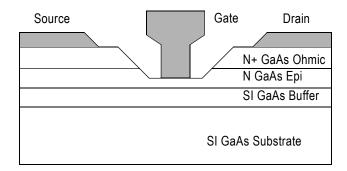

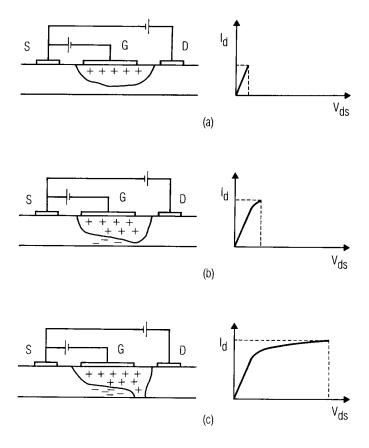

|     | 2.5.1   | MESFET Operation                  | 74  |

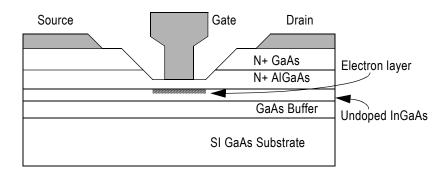

|     | 2.5.2   | HEMT Operation                    | 78  |

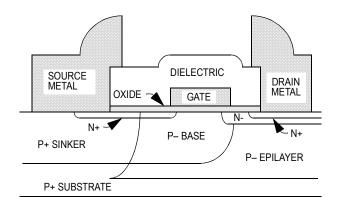

|     | 2.5.3   | MOSFET Operation                  | 79  |

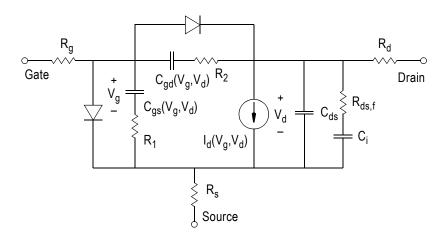

|     | 2.5.4   | MESFET Modeling                   | 81  |

|     | 2.5.5   | HEMT Modeling                     | 86  |

|     | 2.5.6   | MOSFET Modeling                   | 88  |

|     | 2.5.7   | FET Capacitances                  | 90  |

| 2.6 | Bipola  | Devices                           | 95  |

|     | 2.6.1   | BJT Operation                     | 96  |

|     | 2.6.2   | HBT Operation                     | 100 |

|     | 2.6.3   | BJT Modeling                      | 101 |

|     | 2.6.4   | HBT Modeling                      | 104 |

| 2.7 | Therma  | al Modeling                       | 104 |

| 2.8 | Parame  | eter Extraction                   | 108 |

|     | 2.8.1   | Diode Parameter Extraction        | 109 |

| Nonlinear Microwave and | l Kr | Circuit | ٠. |

|-------------------------|------|---------|----|

|-------------------------|------|---------|----|

x

|           |      | 2.8.2    | FET Parameter Extraction                                 | 111 |

|-----------|------|----------|----------------------------------------------------------|-----|

|           |      | 2.8.3    | Parameter Extraction for Bipolar Devices                 | 115 |

|           |      | 2.8.4    | Final Notes on Parameter Extraction                      | 116 |

|           | Refe | rences   |                                                          | 117 |

| Chapter 3 | Harn | nonic-Ba | alance Analysis and Related Methods                      | 119 |

|           | 3.1  | Why U    | Jse Harmonic-Balance Analysis?                           | 119 |

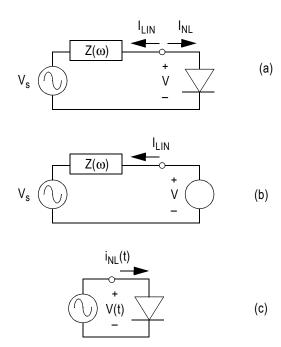

|           | 3.2  |          | uristic Introduction to<br>onic-Balance Analysis         | 120 |

|           | 3.3  | Single   | -Tone Harmonic-Balance Analysis                          | 124 |

|           |      | 3.3.1    | Circuit Partitioning                                     | 124 |

|           |      | 3.3.2    | The Nonlinear Subcircuit                                 | 129 |

|           |      | 3.3.3    | The Linear Subcircuit                                    | 135 |

|           |      | 3.3.4    | Solution Algorithms                                      | 137 |

|           |      | 3.3.5    | Newton Solution of the Harmonic-Balance Equation         | 140 |

|           |      | 3.3.6    | Selecting the Number of Harmonics and Time Samples       | 149 |

|           |      | 3.3.7    | Matrix Methods for Solving (3.37)                        | 151 |

|           |      | 3.3.8    | Norm Reduction                                           | 155 |

|           |      | 3.3.9    | Optimizing Convergence and Efficiency                    | 156 |

|           | 3.4  |          | Signal/Small-Signal Analysis Using rsion Matrices        | 164 |

|           |      | 3.4.1    | Conversion Matrix Formulation                            | 165 |

|           |      | 3.4.2    | Applying Conversion Matrices to Time-Varying Circuits    | 175 |

|           |      | 3.4.3    | Nodal Formulation                                        | 185 |

|           | 3.5  |          | one Excitation and Intermodulation in Timeg<br>GCircuits | 187 |

Contents xi

|           | 3.6   | Multite   | one Harmonic-Balance Analysis                      | 198 |

|-----------|-------|-----------|----------------------------------------------------|-----|

|           |       | 3.6.1     | Generalizing the Harmonic-Balance<br>Concept       | 198 |

|           |       | 3.6.2     | Reformulation and Fourier Transformation           | 200 |

|           |       | 3.6.3     | Discrete Fourier Transforms                        | 201 |

|           |       | 3.6.4     | Almost-Periodic Fourier Transform (APFT)           | 203 |

|           |       | 3.6.5     | Two-Dimensional FFT                                | 204 |

|           |       | 3.6.6     | Artificial Frequency Mapping                       | 205 |

|           |       | 3.6.7     | Frequency Sets                                     | 206 |

|           |       | 3.6.8     | Determining the Jacobian                           | 207 |

|           | 3.7   | Modul     | ated Waveforms and Envelope Analysis               | 209 |

|           |       | 3.7.1     | Modulated Signals                                  | 209 |

|           |       | 3.7.2     | Envelope Analysis                                  | 211 |

|           | Refe  | rences    |                                                    | 212 |

| Chapter 4 | Volte | erra-Seri | es and Power-Series Analysis                       | 215 |

|           | 4.1   | Power-    | -Series Analysis                                   | 216 |

|           |       | 4.1.1     | Power-Series Model and Multitone<br>Response       | 216 |

|           |       | 4.1.2     | Frequency Generation                               | 224 |

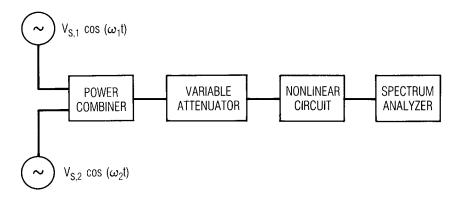

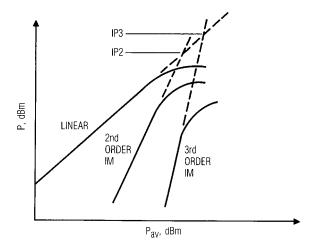

|           |       | 4.1.3     | Intercept Point and Power Relations                | 225 |

|           |       | 4.1.4     | Intermodulation Measurement                        | 231 |

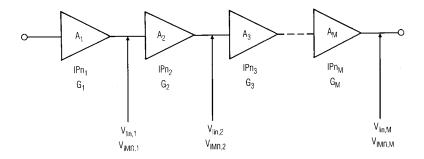

|           |       | 4.1.5     | Interconnections of Weakly Nonlinear<br>Components | 232 |

|           | 4.2   | Volteri   | ra-Series Analysis                                 | 235 |

|           |       | 4.2.1     | Introduction to the Volterra Series                | 235 |

|           |       | 4.2.2     | Volterra Functionals and Nonlinear                 | 237 |

|           |       | 4.2.3    | Determining Nonlinear Transfer Functions<br>by the Harmonic Input Method | 241 |

|-----------|-------|----------|--------------------------------------------------------------------------|-----|

|           |       | 4.2.4    | Applying Nonlinear Transfer Functions                                    | 251 |

|           |       | 4.2.5    | The Method of Nonlinear Currents                                         | 254 |

|           |       | 4.2.6    | Application to Large Circuits                                            | 265 |

|           |       | 4.2.7    | Controlled Sources                                                       | 274 |

|           |       | 4.2.8    | Spectral Regrowth and Adjacent-Channel Power                             | 274 |

|           | Refer | ences    |                                                                          | 276 |

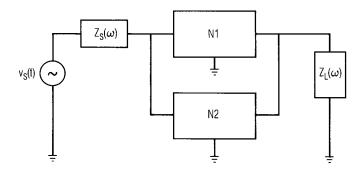

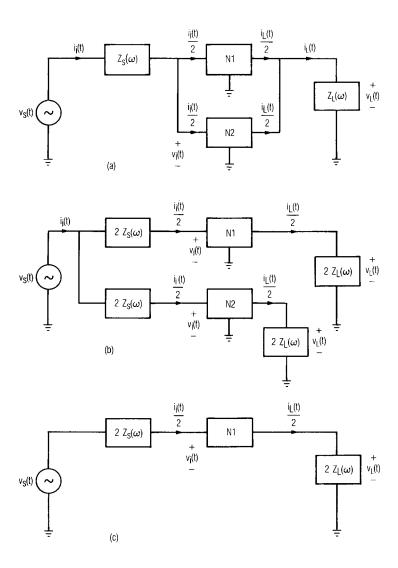

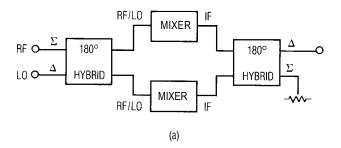

| Chapter 5 | Balar | nced and | Multiple-Device Circuits                                                 | 277 |

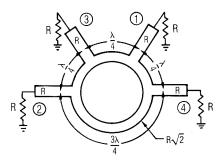

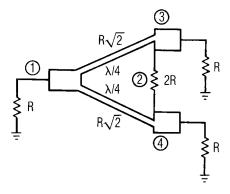

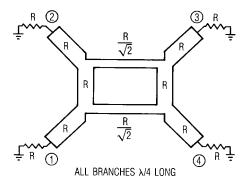

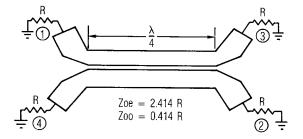

|           | 5.1   | Balance  | ed Circuits Using Microwave Hybrids                                      | 278 |

|           |       | 5.1.1    | Properties of Ideal Hybrids                                              | 278 |

|           |       | 5.1.2    | Practical Hybrids                                                        | 280 |

|           |       | 5.1.3    | Properties of Hybrid-Coupled Components                                  | 288 |

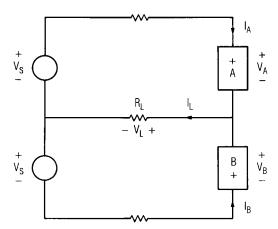

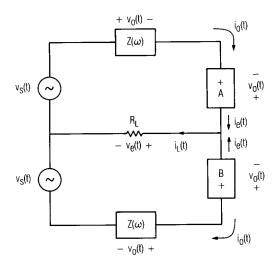

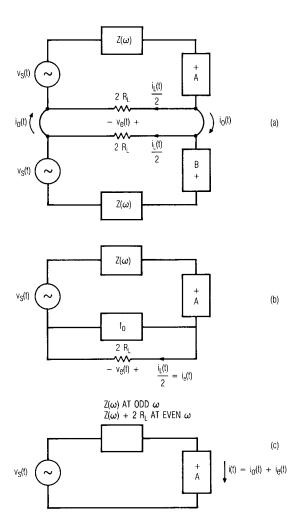

|           | 5.2   | Direct 1 | Interconnection of Microwave Components                                  | 300 |

|           |       | 5.2.1    | Harmonic Properties of Two-Terminal Device Interconnections              | 301 |

|           | Refer | rences   |                                                                          | 315 |

| Chapter 6 | Diode | e Mixers |                                                                          | 317 |

|           | 6.1   | Mixer l  | Diodes                                                                   | 317 |

|           |       | 6.1.1    | Mixer Diode Types                                                        | 318 |

|           | 6.2   | Nonlin   | ear Analysis of Mixers                                                   | 324 |

|           |       | 6.2.1    | Multitone Harmonic-Balance Analysis of Mixers                            | 324 |

|           | 6.3   | Single-  | Diode Mixer Design                                                       | 328 |

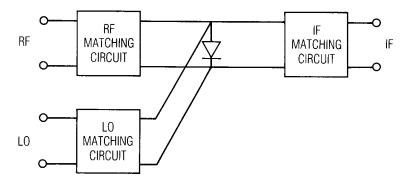

|           |       | 6.3.1    | Design Approach                                                          | 329 |

|           |       | 6.3.2    | Design Philosophy                                                        | 329 |

|           |       | 633      | Diode Selection                                                          | 333 |

| Contents | xiii |  |

|----------|------|--|

|          |      |  |

|           |       | 6.3.4    | de Bias                                               | 335 |

|-----------|-------|----------|-------------------------------------------------------|-----|

|           |       | 6.3.5    | Design Example                                        | 335 |

|           | 6.4   | Balanc   | ed Mixers                                             | 339 |

|           |       | 6.4.1    | Singly Balanced Mixers                                | 339 |

|           |       | 6.4.2    | Singly Balanced Mixer Example                         | 343 |

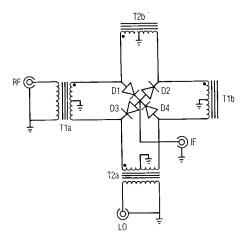

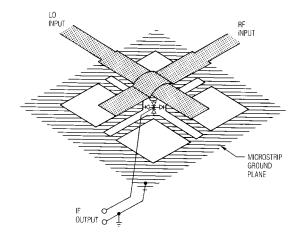

|           |       | 6.4.3    | Doubly Balanced Mixers                                | 345 |

|           | Refer | ences    |                                                       | 354 |

| Chapter 7 | Diode | e Freque | ncy Multipliers                                       | 355 |

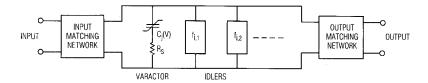

|           | 7.1   | Varacto  | or Frequency Multipliers                              | 356 |

|           |       | 7.1.1    | Noise Considerations                                  | 356 |

|           |       | 7.1.2    | Power Relations and Efficiency<br>Limitations         | 357 |

|           |       | 7.1.3    | Design of Varactor Frequency Multipliers              | 361 |

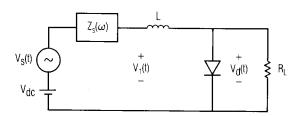

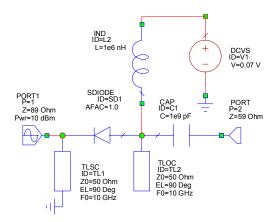

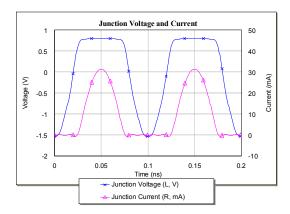

|           |       | 7.1.4    | Design Example of a Varactor Multiplier               | 364 |

|           |       | 7.1.5    | Final Details                                         | 366 |

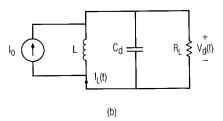

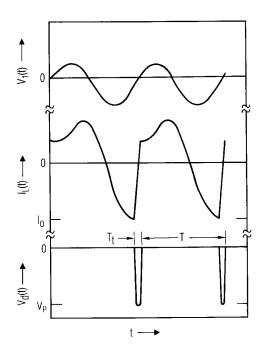

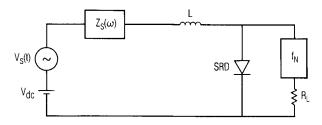

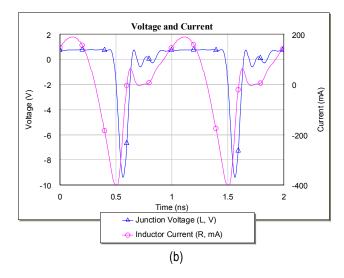

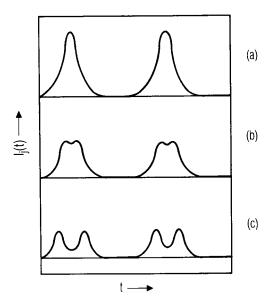

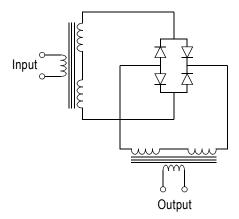

|           | 7.2   | Step-R   | ecovery Diode Multipliers                             | 370 |

|           |       | 7.2.1    | Multiplier Operation                                  | 371 |

|           |       | 7.2.2    | Design Example of an SRD Multiplier                   | 378 |

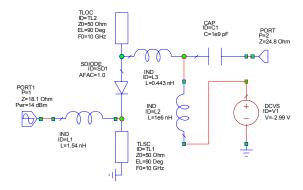

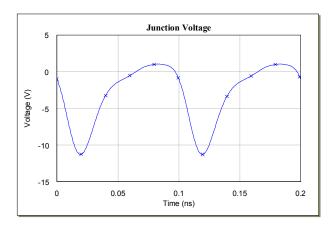

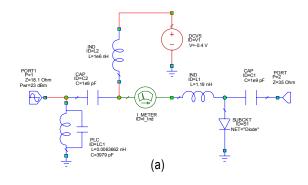

|           |       | 7.2.3    | Harmonic-Balance Simulation of SRD<br>Multipliers     | 381 |

|           | 7.3   | Resisti  | ve Diode Frequency Multipliers                        | 382 |

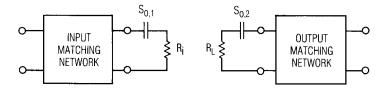

|           |       | 7.3.1    | Approximate Analysis and Design of Resistive Doublers | 382 |

|           |       | 7.3.2    | Design Example of a Resistive Doubler                 | 388 |

|           | 7.4   | Balanc   | ed Multipliers                                        | 391 |

|           | Refer | ences    |                                                       | 392 |

| N | On | linear | Mici | owave | and | RF | Circ | nits |

|---|----|--------|------|-------|-----|----|------|------|

|   |    |        |      |       |     |    |      |      |

xiv

| Chapter 8 | Smal       | ll-Signal | Amplifiers                                                      |     |

|-----------|------------|-----------|-----------------------------------------------------------------|-----|

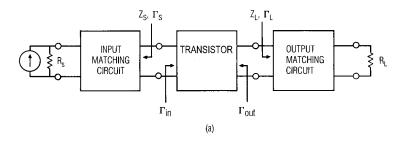

|           | 8.1        | Review    | w of Linear Amplifier Theory                                    | 395 |

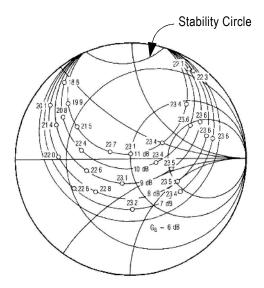

|           |            | 8.1.1     | Stability Considerations in Linear<br>Amplifier Design          | 395 |

|           |            | 8.1.2     | Amplifier Design                                                | 400 |

|           |            | 8.1.3     | Characteristics of FETs and Bipolars in Small-Signal Amplifiers | 405 |

|           |            | 8.1.4     | Broadband Amplifiers                                            | 406 |

|           |            | 8.1.5     | Negative Image Modeling                                         | 407 |

|           | 8.2        | Nonlin    | near Analysis                                                   | 409 |

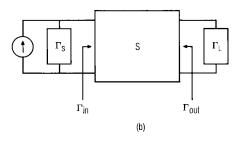

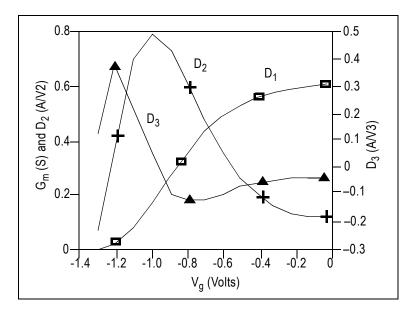

|           |            | 8.2.1     | Nonlinearities in FETs                                          | 410 |

|           |            | 8.2.2     | Nonlinearities in Bipolar Devices                               | 413 |

|           |            | 8.2.3     | Nonlinear Phenomena in Small-Signal<br>Amplifiers               | 415 |

|           |            | 8.2.4     | Calculating the Nonlinear Transfer Functions                    | 421 |

|           | 8.3        | Linear    | ity Optimization                                                | 421 |

|           |            | 8.3.1     | Linearity Criteria                                              | 421 |

|           |            | 8.3.2     | MESFETs and HEMTs                                               | 423 |

|           |            | 8.3.3     | HBTs and BJTs                                                   | 428 |

|           | References |           |                                                                 | 430 |

| Chapter 9 | Powe       | er Ampli  | fiers                                                           | 431 |

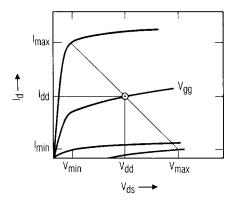

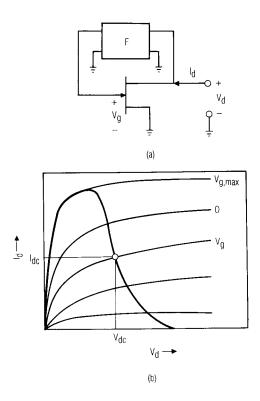

|           | 9.1        | FET a     | nd Bipolar Devices for Power Amplifiers                         | 431 |

|           |            | 9.1.1     | Device Structure                                                | 431 |

|           |            | 9.1.2     | Modeling Power Devices                                          | 434 |

|           | 9.2        | Power     | -Amplifier Design                                               | 439 |

|           |            | 9.2.1     | Class-A Amplifiers                                              | 439 |

|           |            | 922       | Class-B Amplifiers                                              | 443 |

Contents xv

|            |       | 9.2.3              | Other Modes of Operation                                  | 447 |

|------------|-------|--------------------|-----------------------------------------------------------|-----|

|            | 9.3   | Design             | of Solid-State Power Amplifiers                           | 449 |

|            |       | 9.3.1              | Approximate Design of Class-A FET Amplifiers              | 449 |

|            |       | 9.3.2              | Approximate Design of Class-A Bipolar Amplifiers          | 453 |

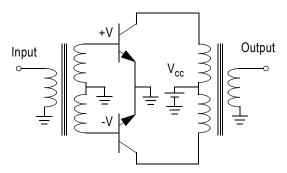

|            |       | 9.3.3              | Approximate Design of Class-B<br>Amplifiers               | 454 |

|            |       | 9.3.4              | Push-Pull Class-B Amplifiers                              | 456 |

|            |       | 9.3.5              | Harmonic Terminations                                     | 456 |

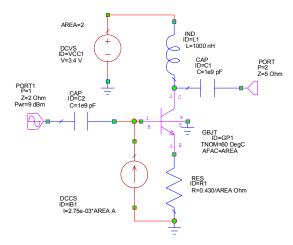

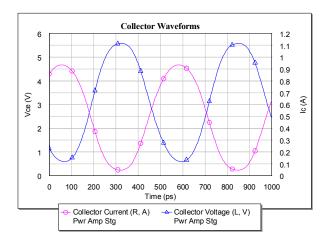

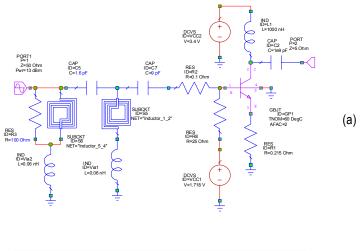

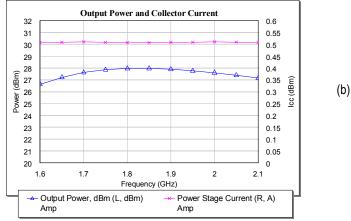

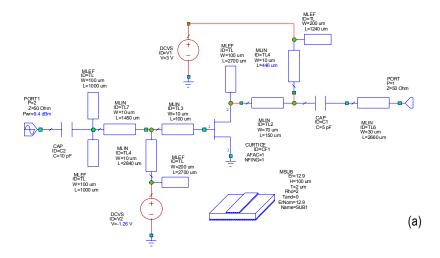

|            |       | 9.3.6              | Design Example: HBT Power Amplifier                       | 457 |

|            | 9.4   | Harmon             | nic-Balance Analysis of Power Amplifiers                  | 462 |

|            |       | 9.4.1              | Single-Tone Analysis                                      | 462 |

|            |       | 9.4.2              | Multitone Analysis                                        | 463 |

|            | 9.5   | Practica<br>Design | al Considerations in Power-Amplifier                      | 465 |

|            |       | 9.5.1              | Low Impedance and High Current                            | 465 |

|            |       | 9.5.2              | Uniform Excitation of Multicell Devices                   | 466 |

|            |       | 9.5.3              | Odd-Mode Oscillation                                      | 467 |

|            |       | 9.5.4              | Efficiency and Load Optimization                          | 467 |

|            |       | 9.5.5              | Back-off and Linearity                                    | 468 |

|            |       | 9.5.6              | Voltage Biasing and Current Biasing in<br>Bipolar Devices | 470 |

|            |       | 9.5.7              | Prematching                                               | 471 |

|            |       | 9.5.8              | Thermal Considerations                                    | 471 |

|            | Refer | ences              |                                                           | 473 |

| Chapter 10 | Activ | e Freque           | ency Multipliers                                          | 475 |

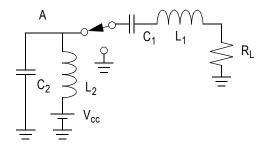

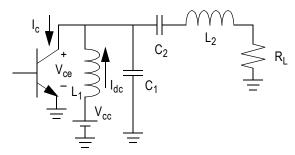

|            | 10.1  | Design             | Philosophy                                                | 475 |

|            | 10.2  | Design             | of FET Frequency Multipliers                              | 477 |

|            |       |                    |                                                           |     |

| Nonl | inear | Microwave | and RF | Circuits |

|------|-------|-----------|--------|----------|

|      |       |           |        |          |

xvi

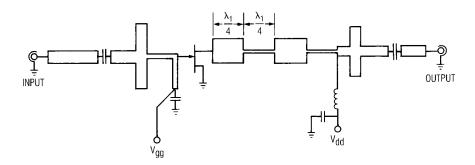

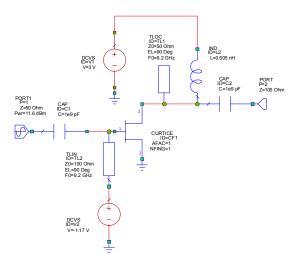

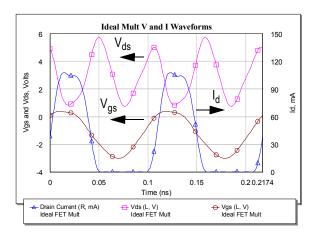

|            |       | 10.2.1  | Design Theory                                               | 477 |

|------------|-------|---------|-------------------------------------------------------------|-----|

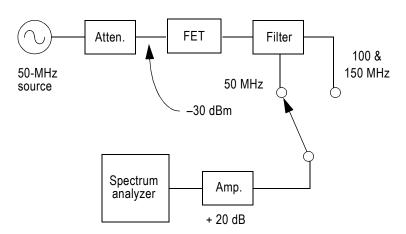

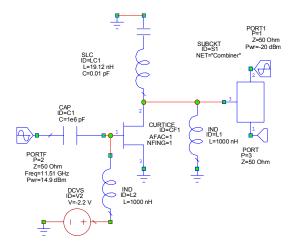

|            |       | 10.2.2  | Design Example: A Simple FET Multiplier                     | 483 |

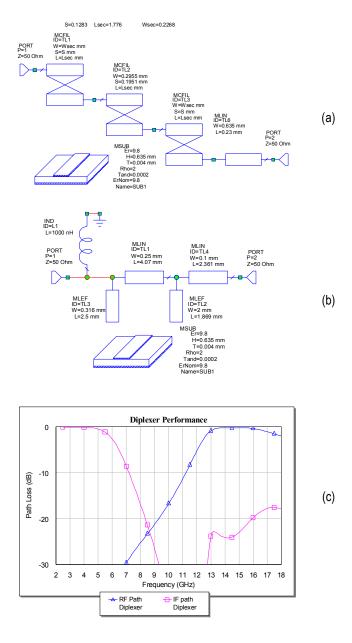

|            |       | 10.2.3  | Design Example: A Broadband Frequency Multiplier            | 487 |

|            |       | 10.2.4  | Bipolar Frequency Multipliers                               | 490 |

|            | 10.3  |         | nic-Balance Analysis of Active<br>ncy Multipliers           | 490 |

|            | 10.4  | Practic | al Considerations                                           | 491 |

|            |       | 10.4.1  | Effect of Gate and Drain Terminations at Unwanted Harmonics | 491 |

|            |       | 10.4.2  | Balanced Frequency Multipliers                              | 491 |

|            |       | 10.4.3  | Noise                                                       | 493 |

|            |       | 10.4.4  | Harmonic Rejection                                          | 494 |

|            |       | 10.4.5  | Stability                                                   | 494 |

|            |       | 10.4.6  | High-Order Multiplication                                   | 495 |

|            | Refer | ences   |                                                             | 495 |

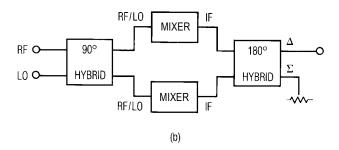

| Chapter 11 | Activ | e Mixer | s and FET Resistive Mixers                                  | 497 |

|            | 11.1  | Design  | of Single-Gate FET Mixers                                   | 497 |

|            |       | 11.1.1  | Design Philosophy                                           | 497 |

|            |       | 11.1.2  | Approximate Mixer Analysis                                  | 501 |

|            |       | 11.1.3  | Bipolar Mixers                                              | 505 |

|            |       | 11.1.4  | Matching Circuits in Active Mixers                          | 506 |

|            |       | 11.1.5  | Nonlinear Analysis of Active Mixers                         | 508 |

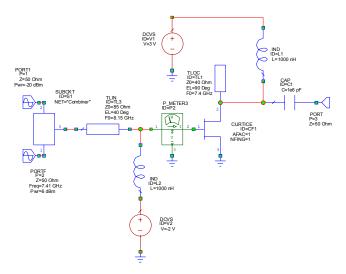

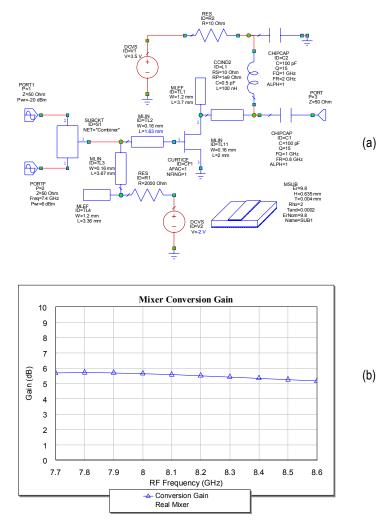

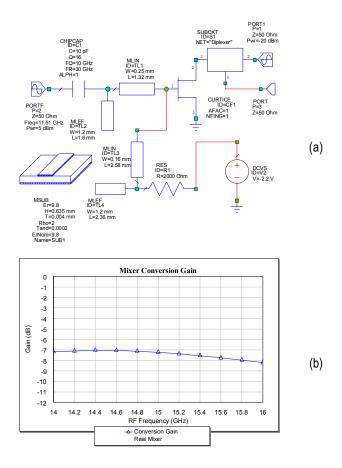

|            |       | 11.1.6  | Design Example: Simple, Active FET Mixer                    | 508 |

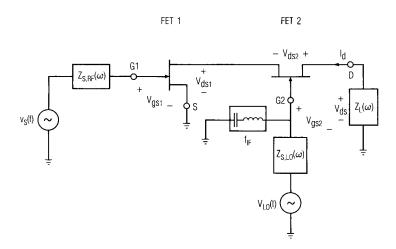

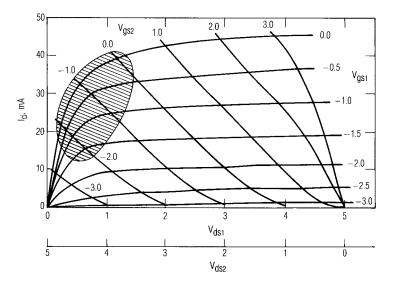

|            | 11.2  | Dual-G  | ate FET Mixers                                              | 510 |

|            | 11.3  | Balance | ed Active Mixers                                            | 515 |

|            |       | 11.3.1  | Singly Balanced Mixers                                      | 515 |

| Contents | xvii |

|----------|------|

| Contents | xvii |

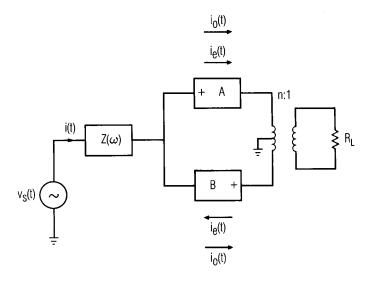

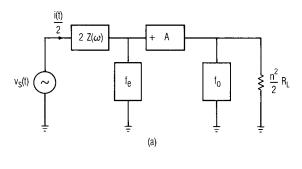

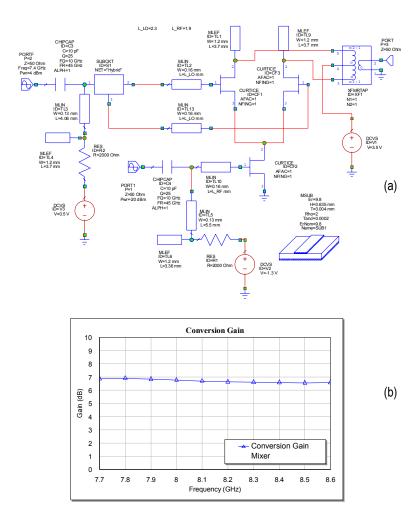

|            |       | 11.3.2                 | Design Example: Computer-Oriented<br>Design Approach | 518 |

|------------|-------|------------------------|------------------------------------------------------|-----|

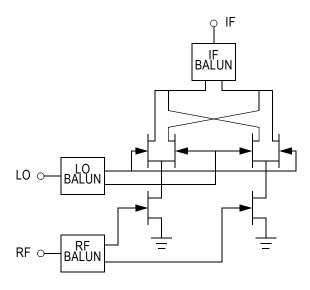

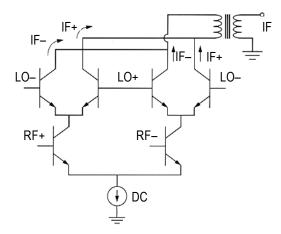

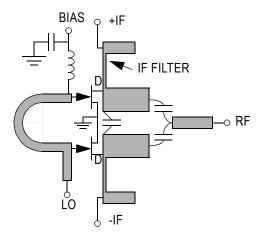

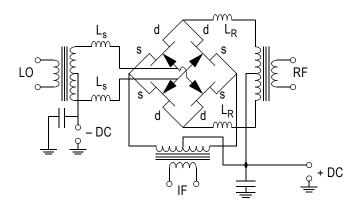

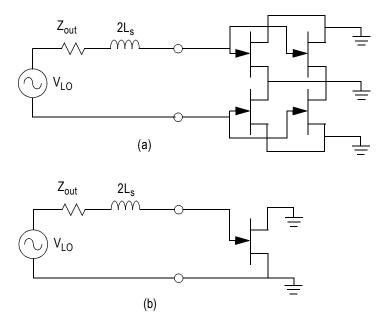

|            |       | 11.3.3                 | Doubly Balanced FET Mixers                           | 520 |

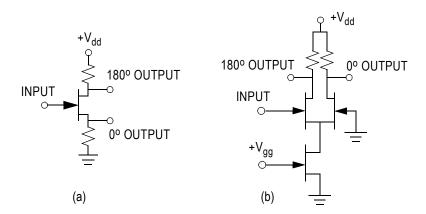

|            |       | 11.3.4                 | Active Baluns                                        | 522 |

|            |       | 11.3.5                 | Gilbert-Cell Mixers                                  | 524 |

|            | 11.4  | FET Re                 | esistive Mixers                                      | 525 |

|            |       | 11.4.1                 | Fundamentals                                         | 526 |

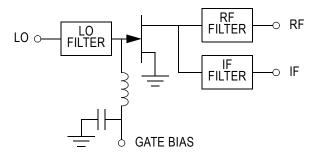

|            |       | 11.4.2                 | Single-FET Resistive Mixers                          | 527 |

|            |       | 11.4.3                 | Design of Single-FET Resistive Mixers                | 528 |

|            |       | 11.4.4                 | Design Example: FET Resistive Mixer                  | 529 |

|            |       | 11.4.5                 | Balanced FET Resistive Mixers                        | 530 |

|            | Refer | ences                  |                                                      | 536 |

| Chapter 12 | Tran  | Transistor Oscillators |                                                      |     |

|            | 12.1  | Classic                | al Oscillator Theory                                 | 537 |

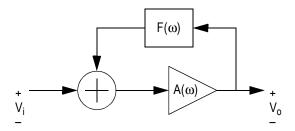

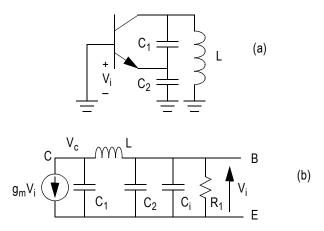

|            |       | 12.1.1                 | Feedback Oscillator Theory                           | 537 |

|            |       | 12.1.2                 | Feedback Oscillator Design                           | 540 |

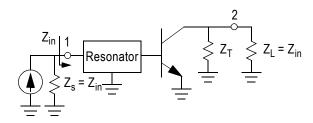

|            |       | 12.1.3                 | Negative-Resistance Oscillation                      | 542 |

|            |       | 12.1.4                 | Negative Resistance in Transistors                   | 545 |

|            |       | 12.1.5                 | Oscillator Design by the Classical Approach          | 549 |

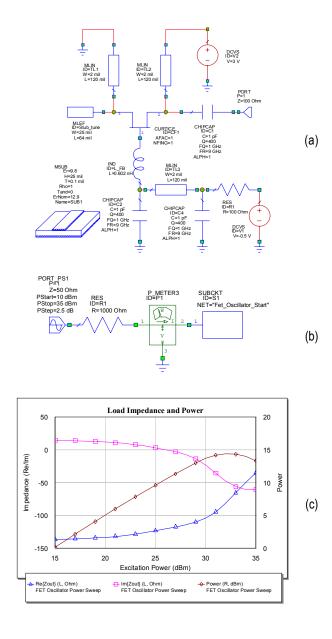

|            | 12.2  | Nonlin                 | ear Analysis of Transistor Oscillators               | 555 |

|            |       | 12.2.1                 | Numerical Device-Line Measurements                   | 556 |

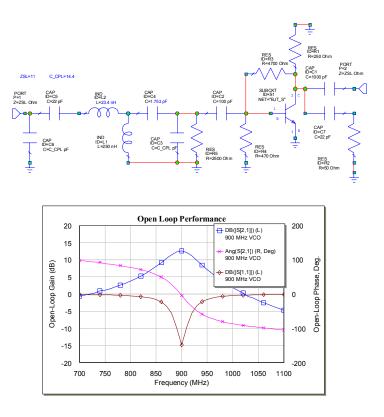

|            |       | 12.2.2                 | Harmonic Balance: Method 1                           | 557 |

|            |       | 12.2.3                 | Harmonic Balance: Method 2                           | 559 |

|            |       | 12.2.4                 | Eigenvalue Formulation                               | 560 |

|            | 12.3  | Practic                | al Aspects of Oscillator Design                      | 562 |

|            |       | 12.3.1                 | Multiple Resonances                                  | 562 |

|            |       | 12.3.2                 | Frequency Stability                                  | 562 |

| xviii            | ear Microwave and RF Circuits |                                |     |

|------------------|-------------------------------|--------------------------------|-----|

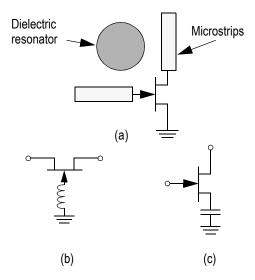

|                  | 12.3.3                        | Dielectric Resonators          | 563 |

|                  | 12.3.4                        | Hyperabrupt Varactors          | 564 |

|                  | 12.3.5                        | Phase Noise                    | 566 |

|                  | 12.3.6                        | Pushing and Pulling            | 573 |

|                  | 12.3.7                        | Post-Tuning Drift              | 573 |

|                  | 12.3.8                        | Harmonics and Spurious Outputs | 573 |

| Refere           | ences                         |                                | 574 |

| About the Author |                               |                                | 575 |

| Index            |                               |                                | 577 |

### **Preface**

Back in the days when I had a lot more energy and a lot less sense, I wrote the first edition of this book. I had just finished writing *Microwave Mixers*, and friends kept asking me, "Well, are you going to write another one?" Sales of *Mixers* were brisk, and the feedback from readers was encouraging, so it was easy to answer, "Sure, why not?" After a year of painful labor, *Nonlinear Microwave Circuits* was born.

The first edition of *Nonlinear Microwave Circuits* was published in 1988. It was well received and continued to sell well, even in a reprint edition, for the next 13 years. Now, it is out of print, and properly so: nonlinear circuit technology has advanced well beyond the material in the first edition of that book. In 1988, general-purpose harmonic-balance simulators had just become available, a workstation computer with an 8-MHz processor and 12 megabytes of memory was the state of the art, cell phones were the size of a shoebox, and the term *microwave bipolar transistor* was an oxymoron. My point isn't that we've come a long way; you know that. My point is that the book was clearly due to be updated.

Nonlinear Microwave Circuits has been almost completely rewritten, mainly to update its specific technical information. The general organization of the book, with the first half presenting theory, and the second design information, is unchanged. A couple of chapters, notably Chapters 4 and 5, are essentially unchanged, for obvious reasons. Chapter 2, on device modeling, is almost twice as long as in the original edition, and I easily could have made it longer. Chapter 3, on harmonic-balance analysis, is likewise much longer. The last seven chapters, which are design oriented, are completely new. In particular, design examples have been modernized, so they show how modern circuit-analysis software can best be exploited to produce first-class components.

Nonlinear Microwave Circuits has become Nonlinear Microwave and RF Circuits, a telling change. A large component of the evolution of high-frequency technology, since the first edition, is the importance of RF, wireless, and cellular systems. These depend strongly on heterojunction bipolar transistors, also a technology that has grown to maturity since the publication of the first edition. Similarly, power MOS devices, VHF/UHF transistors in 1988, are extremely important for power applications in the lower end of the microwave region. Finally, while in 1988 the MESFET was the only real option for microwave transistors, now we have high performance HEMT devices for both power and small-signal applications. These new technologies deserve, and have received, a place in this book.

I have many people to thank for their tolerance and assistance in this project. At the top of the list is my wife of 30 years, Julie, who never once has complained about my late nights in my office. My sons, David and Benjamin, also helped enormously, if only by growing up and leaving home. The whole gang at Applied Wave Research also deserve mention and thanks for discussions that clarified many of the dirty little details of making a nonlinear circuit simulator work the way it should. Finally, I am indebted to my colleagues in the nonlinear circuits business, far too many to list, for sharing the benefits of their hard-won experience.

Steve Maas Long Beach, California January 2003

# Chapter 1

# **Introduction, Fundamental Concepts, and Definitions**

Before we can describe the unique properties of nonlinear microwave circuits and the analytical methods necessary to understand them quantitatively, the author and reader must be certain that they both are speaking the same language. This is no small problem, because many of the terms and concepts inherent in nonlinear circuit theory are completely foreign to linear circuits, and many engineers harbor preconceived ideas about these circuits, ideas that are often not altogether correct. Accordingly, in order to establish a common basis for the following discussions, we begin by folding a few important definitions into an heuristic introduction to microwave nonlinearity.

#### 1.1 LINEARITY AND NONLINEARITY

All electronic circuits are nonlinear: this is a fundamental truth of electronic engineering. The linear assumption that underlies most modern circuit theory is in practice only an approximation. Some circuits, such as small-signal amplifiers, are only very weakly nonlinear, however, and are used in systems as if they were linear. In these circuits, nonlinearities are responsible for phenomena that degrade system performance and must be minimized. Other circuits, such as frequency multipliers, exploit the nonlinearities in their circuit elements; these circuits would not be possible if nonlinearities did not exist. In these, it is often desirable to maximize (in some sense) the effect of the nonlinearities, and even to minimize the effects of annoying linear phenomena. The problem of analyzing and designing such circuits is usually more complicated than for linear circuits; it is the subject of much special concern.

The statement that all circuits are nonlinear is not made lightly. The nonlinearities of solid-state devices are well known, but it is not generally recognized that even passive components such as resistors, capacitors, and inductors, which are expected to be linear under virtually all conditions, are nonlinear in the extremes of their operating ranges. When large voltages or currents are applied to resistors, for example, heating changes their resistances. Capacitors, especially those made of semiconductor materials, exhibit nonlinearity, and the nonlinearity of iron- or ferrite-core inductors and transformers is legendary. Even RF connectors have been found to generate intermodulation distortion at high power levels; the distortion is caused by the nonlinear resistance of the contacts between dissimilar metals in their construction. Thus, the linear circuit concept is an idealization, and a full understanding of electronic circuits, interference, and other aspects of electromagnetic compatibility requires an understanding of nonlinearities and their effects.

Linear circuits are defined as those for which the superposition principle holds. Specifically, if excitations  $x_1$  and  $x_2$  are applied separately to a circuit having responses  $y_1$  and  $y_2$ , respectively, the response to the excitation  $ax_1 + bx_2$  is  $ay_1 + by_2$ , where a and b are arbitrary constants, which may be real or complex, time-invariant or time-varying. This criterion can be applied to either circuits or systems.

This definition implies that the response of a linear, time-invariant circuit or system includes only those frequencies present in the excitation waveforms. Thus, linear, time-invariant circuits do not generate new frequencies. (Time-varying circuits generate mixing products between the excitation frequencies and the frequency components of the time waveform; we'll examine this special case later in greater detail.) As nonlinear circuits usually generate a remarkably large number of new frequency components, this criterion provides an important dividing line between linear and nonlinear circuits.

Nonlinear circuits are often characterized as either *strongly nonlinear* or *weakly nonlinear*. Although these terms have no precise definitions, a good working distinction is that a weakly nonlinear circuit can be described with adequate accuracy by a Taylor series expansion of its nonlinear current/voltage (I/V), charge/voltage (Q/V), or flux/current  $(\phi/I)$  characteristic around some bias current or voltage. This definition implies that the characteristic is continuous, has continuous derivatives, and, for most practical purposes, does not require more than a few terms in its Taylor series. (The excitation level, which affects the number of terms required, also must not be too high.) Additionally, we usually assume that the nonlinearities and RF drive are weak enough that the dc operating point is not perturbed. Virtually all transistors and passive components satisfy this

definition if the excitation voltages are well within the components' normal operating ranges; that is, well below saturation. Examples of components that do not satisfy this definition are strongly driven transistors and Schottky-barrier diodes, because of their exponential I/V characteristics; digital logic gates, which have input/output transfer characteristics that vary abruptly with input voltage; and step-recovery diodes, which have very strongly nonlinear capacitance/voltage characteristics under forward bias. If a circuit is weakly nonlinear, relatively straightforward techniques, such as power-series or Volterra-series analysis, can be used. Strongly nonlinear circuits are those that do not fit the definition of weak nonlinearity; they must be analyzed by harmonic balance or time-domain methods. These circuits are not too difficult to handle if they include only single-frequency excitation or comprise only lumped elements. The most difficult case to analyze is a strongly nonlinear circuit that includes a mix of lumped and distributed components, arbitrary impedances, and multiple excitations.

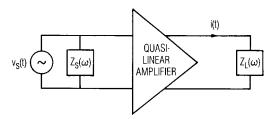

Another useful concept is *quasilinearity*. A quasilinear circuit is one that can be treated for most purposes as a linear circuit, although it may include weak nonlinearities. The nonlinearities are weak enough that their effect on the linear part of the circuit's response is negligible. This does not mean that the nonlinearities themselves are negligible; they may still cause other kinds of trouble. A small-signal transistor amplifier is an example of a quasilinear circuit, as is a varactor-tuned filter.

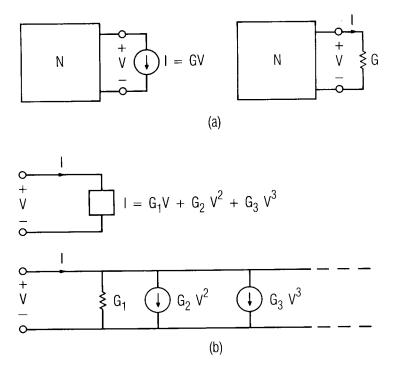

Two final concepts we will employ from time to time are those of twoterminal nonlinearities and transfer nonlinearities. A two-terminal nonlinearity is a simple nonlinear resistor, capacitor, or inductor; its value is a function of one independent variable, the voltage or current at its terminals, called a control voltage or control current. A transfer nonlinearity is a nonlinear controlled source; the control voltage or current is somewhere in the circuit other than at the element's terminals. It is possible for a circuit element to have more than one control, one of which is usually the terminal voltage or current. Thus, many nonlinear elements treated as combinations of transfer and two-terminal nonlinearities. An example of a transfer nonlinearity is the nonlinear controlled current source in the equivalent circuit of a field-effect transistor (FET), where the drain current is a function of the gate voltage. Real circuits and circuit elements often include both types of nonlinearities. An example of the latter is the complete FET equivalent circuit described in Section 2.5.4, including nonlinear capacitors with multiple control voltages, transconductance, and drain-to-source resistance.

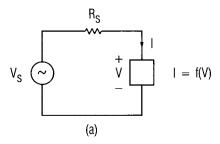

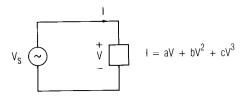

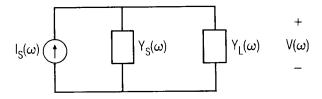

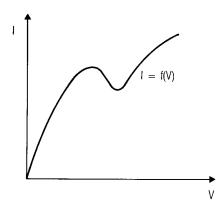

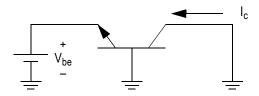

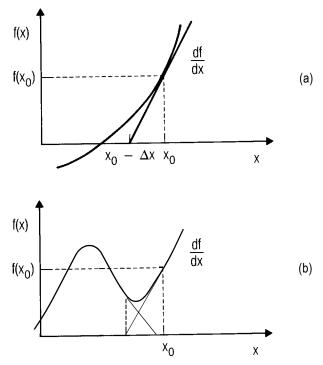

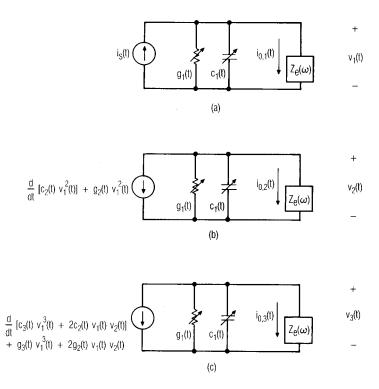

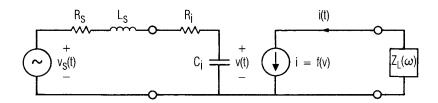

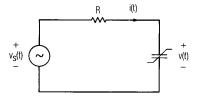

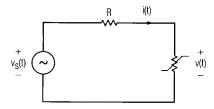

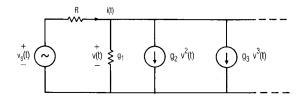

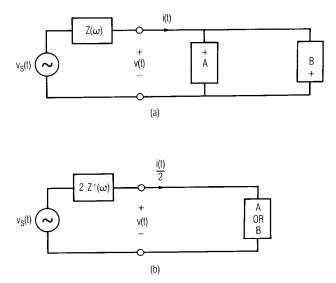

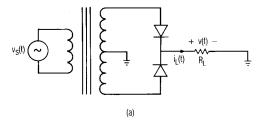

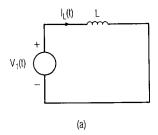

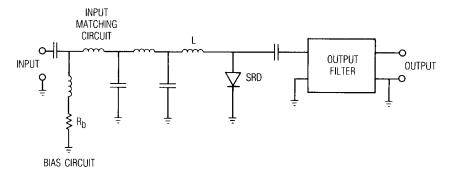

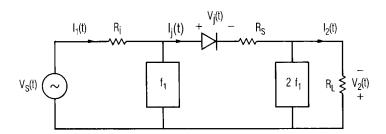

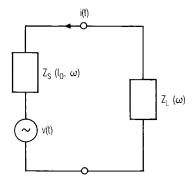

The need to distinguish between the two types of nonlinearities can be illustrated by an example. Consider a nonlinear resistor, Figure 1.1(a), and

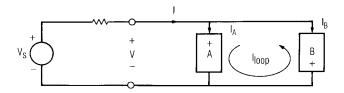

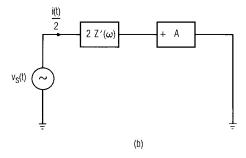

Figure 1.1 (a) Two-terminal nonlinearity; (b) transfer nonlinearity.

a nonlinear but otherwise ideal transconductance amplifier, Figure 1.1(b). Both are excited by a voltage source having some internal impedance  $R_s$ . The amplifier's output current is a function of the excitation voltage and the nonlinear transfer function; the current can be found simply by substituting the voltage waveform into the transfer function. In the two-terminal nonlinearity, however, the excitation voltage generates current components in the nonlinear resistor at new frequencies. These components circulate in the rest of the circuit, generating voltages at those new frequencies across  $R_s$  and therefore across the nonlinear resistor. These new voltage components generate new current components, and current and voltage components at all possible frequencies are generated.

### 1.2 FREQUENCY GENERATION

The traditional way of showing how new frequencies are generated in nonlinear circuits is to describe the component's I/V characteristic by a power series, and to assume that the excitation voltage has multiple frequency components. We will repeat this analysis here, as it is a good intuitive introduction to nonlinear circuits. However, our heuristic

examination will illustrate some frequency-generating properties of nonlinear circuits that are sometimes ignored in the traditional approach, and will introduce some analytical techniques that complement others we will introduce in later chapters.

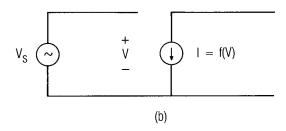

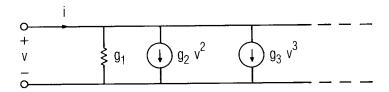

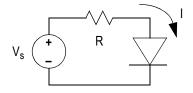

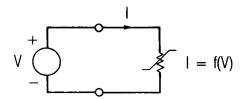

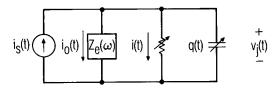

Figure 1.2 shows a circuit with excitation  $V_s$  and a resulting current I. The circuit consists of a two-terminal nonlinearity, but because there is no source impedance,  $V = V_s$ , and the current can be found by substituting the source voltage waveform into the power series. Mathematically, the situation is the same as that of the transfer nonlinearity of Figure 1.1(b).

The current is given by the expression

$$I = aV + bV^2 + cV^3 (1.1)$$

where a, b, and c are constant, real coefficients. We assume that  $V_s$  is a two-tone excitation of the form

$$V_s = v_s(t) = V_1 \cos(\omega_1 t) + V_2 \cos(\omega_2 t)$$

(1.2)

Substituting (1.1) into (1.2) gives, for the first term,

$$i_a(t) = av_s(t) = aV_1\cos(\omega_1 t) + aV_2\cos(\omega_2 t)$$

(1.3)

After doing the same with the second term, the quadratic, and applying the well-known trigonometric identities for squares and products of cosines, we obtain

$$i_b(t) = bv_s^2(t) = \frac{b}{2} \{ V_1^2 + V_2^2 + V_1^2 \cos(2\omega_1 t) + V_2^2 \cos(2\omega_2 t) + 2V_1 V_2 [\cos((\omega_1 + \omega_2)t) + \cos((\omega_1 - \omega_2)t)] \}$$

(1.4)

and the third term, the cubic, gives

**Figure 1.2** Two-terminal nonlinear resistor excited directly by a voltage source.

$$\begin{split} i_c(t) &= c v_s^3(t) = \frac{c}{4} \{ V_1^3 \cos(3\omega_1 t) + V_2^3 \cos(3\omega_1 t) \\ &+ 3 V_1^2 V_2 [\cos((2\omega_1 + \omega_2)t) + \cos((2\omega_1 - \omega_2)t)] \\ &+ 3 V_1 V_2^2 [\cos((\omega_1 + 2\omega_2)t) + \cos((\omega_1 - 2\omega_2)t)] \\ &+ 3 (V_1^3 + 2 V_1 V_2^2) \cos(\omega_1 t) \\ &+ 3 (V_2^3 + 2 V_1^2 V_2) \cos(\omega_2 t) \} \end{split} \tag{1.5}$$

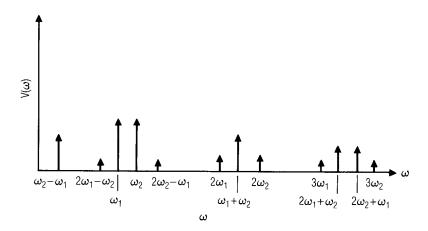

The total current in the nonlinear element is the sum of the current components in (1.3) through (1.5). This is the short-circuit current in the element; it consists of a remarkable number of new frequency components, each successive term in (1.1) generating more new frequencies than the previous one; if a fourth- or fifth-degree nonlinearity were included, the number of new frequencies in the current would be even greater. However, in this case, there are only two frequency components of voltage, at  $\omega_1$  and  $\omega_2$ , because the voltage source is in parallel with the nonlinearity. If there were a resistor between the voltage source and the nonlinearity, even more voltage components would be generated via the currents in that resistor, those new voltage components would generate new current components, and the number of frequency components would be, theoretically, infinite. In order to have a tractable analysis, it then would be necessary to ignore all frequency components beyond some point; the number of components retained would depend upon the strength of the nonlinearity, the magnitude of the excitation voltage, and the desired accuracy of the result. The conceptual and analytical complexity of even apparently simple nonlinear circuits is the first lesson of this exercise.

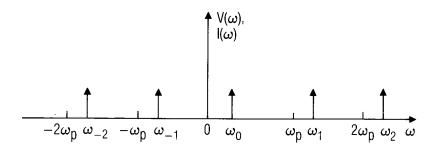

A closer examination of the generated frequencies shows that all occur at a linear combination of the two excitation frequencies; that is, at the frequencies

$$\omega_{m} = m\omega_1 + n\omega_2 \tag{1.6}$$

where m, n = ..., -3, -2, -1, 0, 1, 2, 3, ... The term  $\omega_{m,n}$  is called a *mixing frequency*, and the current component at that frequency (or voltage component, if there were one) is called a *mixing product*. The sum of the absolute values of m and n is called the *order* of the mixing product. For the m, n to be distinct,  $\omega_1$  and  $\omega_2$  must be *noncommensurate*; that is, they are not both harmonics of some single fundamental frequency. We will usually assume that the frequencies are noncommensurate when two or more arbitrary excitation frequencies exist.

An examination of (1.3) through (1.5) shows that a kth-degree term in the power series (1.1) produces new mixing frequencies of order k or below; those mixing frequencies are kth-order combinations of the frequencies of the voltage components at the element's terminals. This does not, however, mean that m + n < k in every nonlinear circuit. In the above example, the terminal voltage components were the excitation voltages, so only two frequencies existed. However, if the circuit of Figure 1.2 included a resistor in series with the nonlinear element, the total terminal voltage would have included not only the excitation frequencies, but higher-order mixing products as well. The nonlinear element then would have generated all possible kth-order combinations of those mixing products and the excitation frequencies. Thus, in general, a nonlinear element can generate mixing frequencies involving all possible harmonics of the excitation frequencies, even those where m + n is greater than the highest power in the power series. It does this by generating kth-order mixing products between all the frequency components of its terminal voltage.

Another conclusion one may draw from (1.3) through (1.5) is that the odd-degree terms in the power series generate only odd-order mixing products, and the even-degree terms generate even-order products. This property can be exploited by balanced structures (Chapter 5). Balanced circuits combine nonlinear elements in such a way that either the even- or odd-degree terms in their power series are eliminated, so only even- or odd-order mixing frequencies are generated. These circuits are very useful in rejecting unwanted even- or odd-order mixing frequencies.

The generation of apparently low-order mixing products from the high-degree terms in (1.1) is worth some examination; the terms at  $\omega_1$  and  $\omega_2$  in (1.5) exemplify this phenomenon. The existence of these terms implies that the fundamental current, for example, is not solely a function of the excitation voltage and the linear term in (1.1); it is dependent on all the odd-degree nonlinearities. Consequently, as  $V_s$  is increased, the cubic term becomes progressively more significant, and the fundamental-frequency

current components either rise more rapidly or level off, depending on the sign of the coefficient c. A closer inspection of these terms shows that they can be considered to have arisen from the kth-degree term as kth-order mixing products; for example, the  $\omega_1$  terms in (1.5) arise as the third-order combinations

$$\omega_1 = \omega_1 + \omega_1 - \omega_1 = \omega_1 + \omega_2 - \omega_2 \tag{1.7}$$

The presence of the negative frequencies might be more convincing if the cosine functions were expressed in their exponential form,  $\cos(\omega t) = (\exp(j\omega t) + \exp(-j\omega t))/2$ . Thus, when dealing with nonlinear circuits, one must always use a system of analysis that does not exclude the presence of negative frequencies.

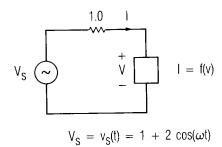

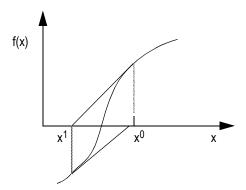

It is worthwhile to consider some specific examples, in order to introduce one approach to nonlinear analysis and to gain further insights into the behavior of nonlinear circuits. Figure 1.3 shows a nonlinear circuit consisting of a resistive nonlinearity and a voltage source. The I/V nonlinearity includes only odd-degree terms:

$$I = f(V) = \frac{V}{2} + \frac{V^3}{7} + \frac{V^5}{15}$$

(1.8)

The  $1\Omega$  resistor complicates things somewhat, but the current can still be found via power-series techniques. First, we use a series reversion to find the voltage as a function of the current:

$$V = f^{-1}(I) = 2.0I - 2.286I^3 + 3.570I^5 + 3.184I^7 + \dots$$

(1.9)

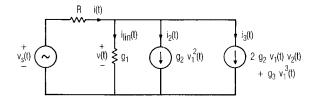

**Figure 1.3** A nonlinear resistor, an excitation source, and a linear series resistor.

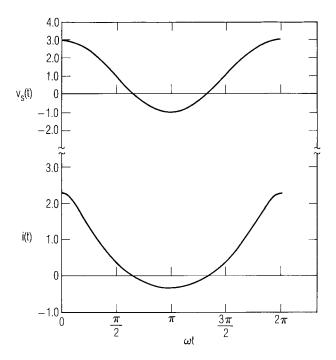

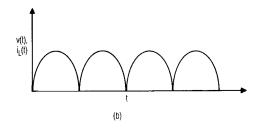

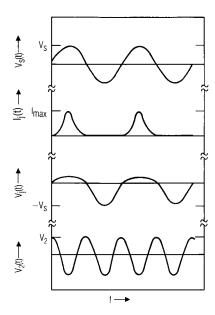

**Figure 1.4** Voltage and current waveforms in the circuit of Figure 1.3.

The formula for the series reversion can be found in Abramowitz [1.1, p. 16]. The voltage across the resistor is  $1 \cdot I$ . Adding this to (1.9) (via Kirchoff's voltage law), we obtain

$$V_s = 3.0I - 2.286I^3 + 3.570I^5 + 3.184I^7 + \dots$$

(1.10)

Performing the reversion again gives, for the current,

$$I = 0.333 V_s + 0.02822 V_s^3 + 0.002271 V_s^5 - 0.001375 V_s^7 + \dots$$

(1.11)

Equation (1.11) expresses I in terms of the known excitation,  $V_s$ . It includes only odd terms because all the circuit elements, the nonlinear and linear resistors, have only odd terms in their power series. (We can view the linear resistor as a special case of a nonlinear resistor, having a one-term power "series".) The series in (1.11) is infinite, but it has been truncated after the seventh-degree term; the series does, in fact, include all odd harmonics, thus all odd-order mixing products. To illustrate this point,

we assume that  $V_s = v_s(t) = 1 + 2\cos(\omega t)$ ;  $v_s(t)$  and the resulting i(t) waveform are shown in Figure 1.4, where the presence of harmonics in the current waveform is evident from its obviously nonsinusoidal shape. The actual harmonics could be found by substituting the expression  $v_s(t) = 1 + 2\cos(\omega t)$  into (1.11) and by applying the same algebra as in (1.1) through (1.5). It is also evident at a glance that the dc component of the current is much greater than 0.364A, the current that would be generated by the dc source alone if the ac source were zero. One must not forget that one of the low-order mixing frequencies generated by high-degree nonlinearities is a dc component; thus, the excitation of a nonlinear circuit may offset its dc operating point.

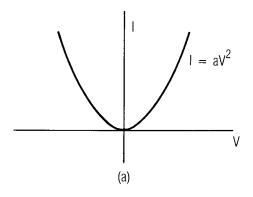

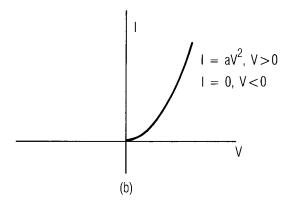

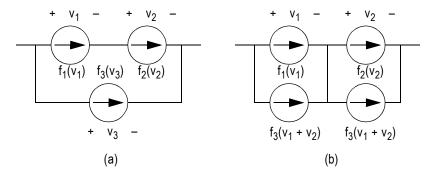

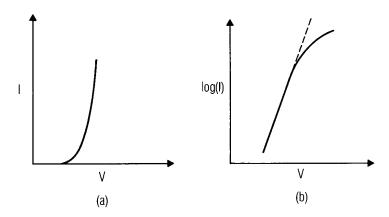

**Figure 1.5** (a) I/V characteristic of the ideal square-law device; (b) I/V characteristic of a real "square-law" device.

As a second example, consider again the circuit of Figure 1.3 with

$$f(V) = aV^2 \tag{1.12}$$

where a is a constant, as shown in Figure 1.5. Equation (1.12) describes an ideal square-law device. This is a strange situation at the outset, for two reasons: first, the series reversion cannot be applied to (1.12); second, because the squared term generates only even-order mixing products, and the excitation frequency is a first- (i.e., odd-) order mixing product, no excitation-frequency current is possible! It is possible that a true squarelaw device could be made; however, it would be unstable, because its incremental resistance at some bias voltage  $V_0$ , df(V) / dV,  $V = V_0$ , would be negative when  $V_0 < 0$ . Practical two-terminal "square-law" elements employ solid-state devices and have I/V characteristics like that shown in Figure 1.5(b); the current follows a square law when V > 0 but is zero when V < 0. This characteristic still presents some analytical problems, because its I/V characteristic has a discontinuous derivative at V = 0. The device could, in concept, be operated in such a way that the voltage is always greater than zero, by biasing it at a value  $V_0$  great enough that no negative excitation peaks can drive the terminal voltage to zero. Its power series then becomes

$$f(v + V_0) = a(v + V_0)^2 = a(V_0^2 + 2V_0v + v^2)$$

(1.13)

where a, again, is a constant, and v is the voltage deviation from the bias point. Equation (1.13) includes the linear term  $2V_0v$ . Thus, it is rarely possible, in practice, to obtain a true square-law device, or, for that matter, a device having only even-degree terms in its power series; practical devices invariably have at least one odd-order term in their power series. This generalization applies to many devices that are often claimed to be square-law devices, such as FETs.

Now that the pure square-law device has been ignominiously unmasked and shown to be a banal multiterm nonlinearity in disguise, it is interesting to see what happens to the circuit of Figure 1.3 when the nonlinearity includes even-degree terms, plus one odd-degree term, the linear one. By choosing the coefficients carefully, one can define the characteristic over any arbitrary range without generating negative resistances. We assume that

$$I = f(V) = V + 2V^2 + 3V^3 \tag{1.14}$$

After series reversion, and including the  $1\Omega$  resistor, we have

$$V_s = 2I - 2I^2 + 8I^3 - 43I^4 + 260I^5 + \dots$$

(1.15)

which has all powers of I. Repeating the reversion again to obtain an expression for I in terms of  $V_s$  clearly results in a series having all powers of  $V_s$ . Thus, even though the original series contained only one odd-degree term (the linear one), the current contains mixing frequencies of all orders, even and odd, including those orders greater than four, the degree of the original power series.

In summary, the I/V characteristic of a nonlinear circuit or circuit element often can be characterized by a power series. The kth-degree term in the series generates kth-order mixing products of the frequencies in its control voltage or current. Some of these may coincide with lower-order frequencies. Mixing products may also coincide with higher-order frequencies; these are generated as kth-order mixing products between other mixing products. Thus, in general a nonlinear circuit having both even- and odd-degree nonlinearities in its power series generates all possible mixing frequencies, regardless of the maximum degree of its nonlinearities.

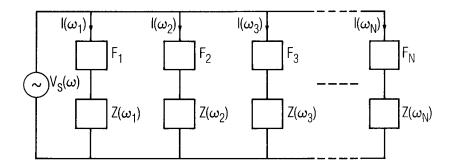

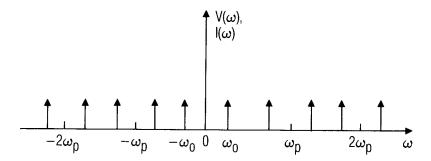

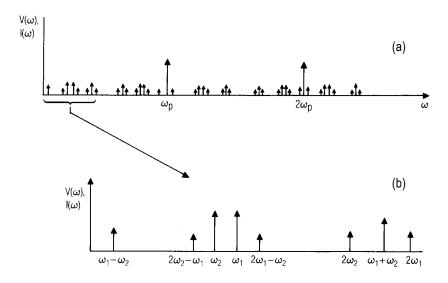

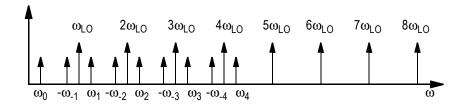

A special case of the nonlinear circuit having two-tone excitation occurs where one tone is relatively large, and the other is vanishingly small. This situation is encountered in microwave mixers, where the large tone is the local oscillator (LO), and the small one is the RF excitation. Because the RF excitation is very small, its harmonics are negligibly small, and we can assume that only its fundamental-frequency component exists. The resulting frequencies are

$$\omega = \omega_{RF} + n\omega_{LO} \tag{1.16}$$

which can also be expressed by our preferred notation,

$$\omega_n = \omega_0 + n\omega_{\rm LO} \tag{1.17}$$

where n = ..., -3, -2, -1, 0, 1, 2, 3, ... and  $\omega_0 = |\omega_{RF} - \omega_{LO}|$  is the mixing frequency closest to dc; in a mixer,  $\omega_0$  is often the intermediate frequency (IF), the output frequency. In (1.16) and (1.17) the mixing frequencies are above and below each LO harmonic, separated by  $\omega_0$ .

If the total small-signal voltage v(t) is much smaller than the LO voltage  $V_L(t)$ , the circuit can be assumed to be linear in the RF voltage. The

total large-signal and small-signal current I(t) in the nonlinearity of (1.1) is given by

$$I(t) = a(v(t) + V_L(t)) + b(v(t) + V_L(t))^2 + c(v(t) + V_L(t))^3$$

(1.18)

Separating the small-signal part of (1.18), and assuming that  $v^2(t) \ll v(t)$ , we find the small-signal current i(t) to be

$$i(t) \approx av(t) + 2bV_L(t)v(t) + 3cV_L^2(t)v(t) + \dots$$

(1.19)

This is a linear function of v, even though many of the current components in (1.19) are at frequencies other than the RF. Thus, a microwave mixer, which has an input at RF and output at, for example,  $\omega_0$ , is a quasilinear component in terms of its input/output characteristics under small-signal excitation.

#### 1.3 NONLINEAR PHENOMENA

The examination of new frequencies generated in nonlinear circuits does not tell the whole story of nonlinear effects, especially the effects of nonlinearities on microwave systems. Many types of nonlinear phenomena have been defined; the foregoing power series techniques can show how these arise from the nonlinearities in individual components or circuit elements. The phenomena described in this section are often considered to be entirely different; we shall see, however, that they are simply manifestations of the same nonlinearities.

#### 1.3.1 Harmonic Generation

One obvious property of a nonlinear system is its generation of harmonics of the excitation frequency or frequencies. These are evident as the terms in (1.3) through (1.5) at  $m\omega_1$ ,  $m\omega_2$ . The *m*th harmonic of an excitation frequency is an *m*th-order mixing frequency. In narrow-band systems, harmonics are not a serious problem because they are far removed in frequency from the signals of interest and inevitably are rejected by filters. In others, such as transmitters, harmonics may interfere with other communications systems and must be reduced by filters or other means.

#### 1.3.2 Intermodulation Distortion

All the mixing frequencies in (1.3) through (1.5) that arise as linear combinations of two or more tones are often called intermodulation (IM) products. IM products generated in an amplifier or communications receiver often present a serious problem, because they represent spurious signals that interfere with, and can be mistaken for, desired signals. IM products are generally much weaker than the signals that generate them; however, a situation often arises wherein two or more very strong signals, which may be outside the receiver's passband, generate an IM product that is within the receiver's passband and obscures a weak, desired signal. Even-order IM products usually occur at frequencies well above or below the signals that generate them, and consequently are often of little concern. The IM products of greatest concern are usually the third-order ones that occur at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$ , because they are the strongest of all oddorder products, are close to the signals that generate them, and often cannot be rejected by filters. Intermodulation is a major concern in microwave systems.

### 1.3.3 Saturation and Desensitization

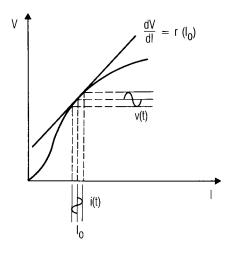

The excitation-frequency current component in the nonlinear circuit examined in Section 1.2 was a function of power series terms other than the linear one; recall that (1.5) included components at  $\omega_1$  and  $\omega_2$  that varied as the cube of signal level. Such components are responsible for gain reduction and desensitization in the presence of strong signals.

In order to describe saturation, we refer to (1.1) to (1.5). From (1.3) and (1.5), and with  $V_2 = 0$ , we find the current component at  $\omega_1$ , designated  $i_1(t)$ , to be

$$i_1(t) = \left(aV_1 + \frac{3}{4}cV_1^3\right)\cos(\omega_1 t)$$

(1.20)

If the coefficient c of the cubic term is negative, the response current saturates; that is, it does not increase at a rate proportional to the increase in excitation voltage. Saturation occurs in all circuits because the available output power is finite. If a circuit such as an amplifier is excited by a large and a small signal, and the large signal drives the circuit into saturation, gain is decreased for the weak signal as well. Saturation therefore causes a decrease in system sensitivity, called *desensitization*.

#### 1.3.4 Cross Modulation

Cross modulation is the transfer of modulation from one signal to another in a nonlinear circuit. To understand cross modulation, imagine that the excitation of the circuit in Figure 1.1 is

$$V_s = v_s(t) = V_1 \cos(\omega_1 t) + (1 + m(t))\cos(\omega_2 t)$$

(1.21)

where m(t) is a modulating waveform; |m(t)| < 1. Equation (1.21) describes a combination of an unmodulated carrier and an amplitude-modulated signal. Substituting (1.21) into (1.1) gives an expression similar to (1.5) for the third-degree term, where the frequency component in  $i_c(t)$  at  $\omega_1$  is

$$i_c'(t) = \frac{3}{2}cV_1V_2^2(1+2m(t)+m^2(t))\cos(\omega_1 t)$$

(1.22)

where a distorted version of the modulation of the  $\omega_2$  signal has been transferred to the  $\omega_1$  carrier. This transfer occurs simply because the two signals are simultaneously present in the same circuit, and its seriousness depends most strongly upon the magnitude of the coefficient c and the strength of the interfering signal  $\omega_2$ . Cross modulation is often encountered on an automobile AM radio when one drives past the transmission antennas of a radio station; the modulation of that station momentarily appears to come in on top of every other received signal.

#### 1.3.5 AM-to-PM Conversion

AM-to-PM conversion is a phenomenon wherein changes in the amplitude of a signal applied to a nonlinear circuit cause a phase shift. This form of distortion can have serious consequences if it occurs in a system in which the signal's phase is important; for example, phase- or frequency-modulated communication systems. The response current at  $\omega_1$  in the nonlinear circuit element considered in Section 1.2 is, from (1.3) and (1.5),

$$i_1(t) = \left(aV_1 + \frac{3}{4}cV_1^3\right)\cos(\omega_1 t)$$

(1.23)

where  $i_1(t)$  is the sum of first- and third-order current components at  $\omega_1$ . Suppose, however, these components were not in phase. This possibility is not predicted by (1.1) through (1.5) because these equations describe a

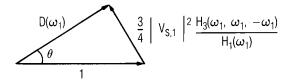

memoryless nonlinearity. In a circuit having reactive nonlinearities, however, it is possible for a phase difference to exist. The response is then the vector sum of two phasors,

$$I_1(\omega_1) = aV_1 + \frac{3}{4}cV_1^3 \exp(j\theta)$$

(1.24)

where  $\theta$  is the phase difference. Even if  $\theta$  remains constant with amplitude, the phase of  $I_1$  changes with variations in  $V_1$ . It is clear from comparing (1.24) to (1.20) that AM-to-PM conversion is most serious as the circuit is driven into saturation

#### 1.3.6 Spurious Responses

At the end of Section 1.2 we saw that a mixer, with an RF input at  $\omega_{RF}$  and an LO at  $\omega_{LO}$ , has currents at the frequencies given by (1.16) or (1.17). It is easy to see that, if the RF is applied at any of those mixing frequencies, currents at all the rest are generated as well. Thus the mixer has some response at a large number of frequencies, not just the one at which it is designed to work. In fact, if the applied signal is very strong, its harmonics are generated and the mixer has spurious responses at any frequency that satisfies the relation

$$\omega_{\rm IF} = m\omega_{\rm RF} + n\omega_{\rm LO} \tag{1.25}$$

where m and n can both be either positive or negative integers. Comparing (1.25) to (1.6) shows that spurious responses are a form of two-tone intermodulation wherein one of the tones is the LO. In microwave technology the concept of spurious responses is used only in reference to mixers.

# 1.3.7 Adjacent Channel Interference

In many communications systems, especially those used for cellular telephones and other forms of telecommunications, modulated signals are squeezed into narrow, contiguous channels. Nonlinear distortion can generate energy that falls outside the intended channel. This is called adjacent-channel interference, spectral regrowth, or sometimes co-channel interference.

Adjacent-channel interference is fundamentally odd-order intermodulation distortion, and, like most odd-order IM, it is dominated by thirdorder effects, although higher-order nonlinearities may also contribute. The phenomenon is easy to understand. Volterra analysis (Chapter 4) of a weakly nonlinear, third-order system shows that the output is simply the sum of all possible third-order intermodulation products involving any three-fold combination of excitation frequency components. Like simple third-order intermodulation involving two excitation tones, many of these components fall close to the original excitation spectrum. These components cause adjacent-channel interference. Many components can also fall within the excitation channel as well, distorting the modulated signal.

#### 1.4 APPROACHES TO ANALYSIS

One of the delights of the last decade or two has been the development of a theoretically sound approach to the analysis of nonlinear microwave circuits, and computer software that implements those methods. Previous techniques were questionable attempts to bend linear theory to nonlinear applications, were highly approximate, or were attempts at "black box" characterizations that did not include everything necessary to obtain correct results. Because some of these older methods (and the ideas they are based on) are still in use, it's worthwhile to take a brief look at some of the dominant methods, and to examine their validity.

#### 1.4.1 Load Pull

One straightforward way to characterize a large-signal circuit, such as an amplifier, is to plot on a Smith chart the contours of its load impedances that result in prescribed values of gain and output power. These approximately circular contours can then be used to select an output load impedance that represents the best trade-off of gain against output power. The contours are generated empirically by connecting various loads to the amplifier and by measuring the gain and output power at each value of load impedance. This process, called *load pulling*, has many limitations; the most serious practical one is the difficulty of measuring the load impedances at the device terminals. Load pulling has a major theoretical problem as well: the load impedance at harmonics of the excitation frequency can significantly affect circuit performance, but load pulling is concerned primarily with the load impedance at the fundamental frequency. Furthermore, load pulling is not useful for determining other important properties of nonlinear or quasilinear circuits, for example, harmonic levels or the effects of multitone excitation.

Modern load-pull systems have overcome many of these limitations. Accurate calibration methods have been developed, as have been "harmonic load-pull" systems that account for harmonic tuning as well as fundamental frequency. Such systems can be valuable tools for designing and characterizing power devices. Still, there is need of a design process that does not require, at the outset, the user to make complicated and expensive measurements on his power transistors.

#### 1.4.2 Large-Signal Scattering Parameters

Another approach to the analysis of large-signal, nonlinear circuits is to measure a set of two-port parameters, usually Scattering parameters (called *S parameters*), at the large-signal excitation level. The standard small-signal equations for S-parameter design are then used to predict the performance characteristics of the circuit. This approach may have limited success if the circuit or device is not very strongly nonlinear, and if it is not applied where it is obviously unsuited; for example, to frequency multipliers. Two-port parameters are fundamentally a *linear* concept, however, so the large-signal S-parameter approach represents a futile attempt to force nonlinear circuits to obey linear circuit theory.

In order to see just one example of the problems that arise from bending linear concepts to fit nonlinear problems, consider the meaning of the output reflection coefficient,  $S_{22}$ , of a FET or bipolar transistor. For large-signal S-parameter analysis,  $S_{22}$  is measured by applying an incident wave to the output port at a power level comparable to that at which the device is used. Now imagine that the device is driven hard at its input, and that the output reflection coefficient is again measured (ignore for a moment the obvious practical difficulties of making such a measurement). If the amplifier is significantly nonlinear, which in all likelihood it will be, one can hardly expect the reflection coefficient to be the same under these conditions, or over the wide range of incident power levels the device is likely to encounter. However, the S-parameter concept is based on the assumption at the that it will be the same.

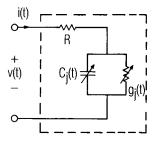

Nevertheless, it is possible to define a large-signal driving point impedance that is valid for matching a source to the input of a nonlinear circuit. It is defined in the same manner as a linear impedance:

$$Z_{\rm in}(\omega) = \frac{V(\omega)}{I(\omega)}$$

(1.26)

where  $V(\omega)$  and  $I(\omega)$  are the voltage and current components at the device terminals and at the excitation frequency  $\omega$ . Other harmonics or mixing products are ignored in determining  $Z_{\rm in}(\omega)$ . Because the circuit is nonlinear,  $Z_{\rm in}(\omega)$  is, in general, a function of the excitation level. We shall use this concept to determine port impedances in the design of many kinds of components described in later chapters.

### 1.4.3 Time-Domain (Transient) Analysis

An intermediate approach, which is theoretically valid and is frequently used for low-frequency analog and digital design, is to use time-domain techniques. It is a straightforward matter to write time-domain differential equations that describe a nonlinear circuit. Those differential equations are nonlinear, but they can be solved numerically. Although time-domain techniques are most practical for analyzing lumped-element circuits, a limited variety of distributed elements can be used as well. Time-domain analysis is not well suited when components are characterized in the frequency domain. The two major limitations of time-domain analysis are its inability to handle frequency-domain quantities (in particular, S parameters) in any practical way, its difficulty in dealing with transmission lines, and the difficulty of applying it to circuits having multiple noncommensurate excitation frequencies.

# 1.4.4 Frequency-Domain Methods

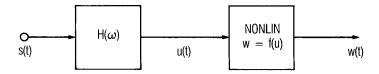

Many frequency-domain techniques for analyzing microwave circuits have become popular in recent years. The two most important are called harmonic-balance analysis and Volterra-series analysis. Harmonic-balance analysis is applicable primarily to strongly nonlinear circuits excited by a single large-signal source; it can be applied to such circuits as transistor power amplifiers, mixers, and frequency multipliers using either diodes or transistors. Volterra-series analysis is applicable to the opposite problem: weakly driven, weakly nonlinear circuits having multiple small-signal excitations at noncommensurate frequencies. As such, it is most useful for evaluating intermodulation characteristics and other nonlinear phenomena in small-signal receiver circuits, especially in amplifiers. With some modifications, the Volterra series can also be used to determine the IM properties of time-varying circuits such as mixers; similarly, harmonicbalance can be extended to certain situations involving noncommensurate signals. Demystifying the theory and practical use of these two techniques is the primary subject of this book.

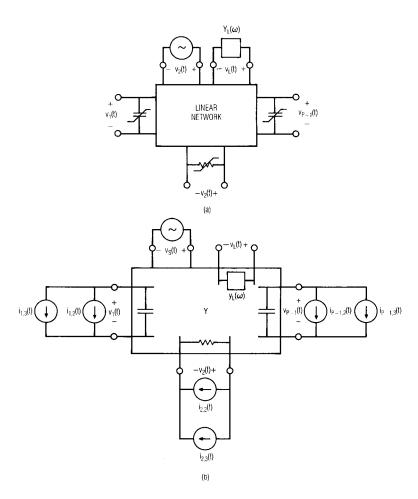

**Figure 1.6** Circuit having a matched source and load, illustrating the concept of available power.

#### 1.4.5 The Quasistatic Assumption

All three methods—time-domain analysis, harmonic-balance analysis, and the Volterra series—require a circuit model consisting of lumped components and, for the latter two, impedance elements or multiports. Solid-state device models must consist of linear or nonlinear capacitors, inductors, resistors, and voltage or current sources (nonlinear inductors can be accommodated, although they are rarely encountered in solid-state microwave devices or circuits). Underlying all the nonlinear models described in this book is the quasistatic assumption, whereby all nonlinear elements are assumed to change instantaneously with changes in their control voltages. This assumption is also implicit in linear circuit theory; it requires, for example, the charge on a capacitor to be a function solely of the voltage at its terminals. If the capacitor is nonlinear, its incremental capacitance, as well as its charge, must change instantaneously with control voltage. A quasistatic circuit is not necessarily memoryless; a memoryless circuit is one in which no charge or magnetic flux storage elements (no capacitors or inductors) exist, so voltages and currents at any instant do not depend upon previous values of voltage or current. In a quasistatic circuit, the network voltages and currents may depend upon previous values of other voltages or currents, but the capacitances, inductances, resistances, and controlled sources do not depend directly upon their own histories.

The quasistatic assumption is critical to the entire business of both linear and nonlinear circuit analysis. It allows one, for example, to devise equivalent circuits for solid-state devices using only lumped linear and nonlinear elements, and makes many of the techniques of linear circuit theory applicable to at least the linear parts of nonlinear circuits. One of the nicest things about the quasistatic assumption is its range of validity.

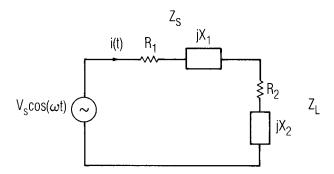

Figure 1.7 Circuit having an unmatched source and load.

Theoretical and experimental studies of silicon and gallium arsenide semiconductors and devices show that time-delay phenomena are usually on the order of picoseconds, or are short compared to the inverse of the highest frequency at which any sensible person would attempt to use the device. Furthermore, the prohibition of time delays is not absolute; in some cases they can still be managed, although with considerably greater difficulty.

#### 1.5 POWER AND GAIN DEFINITIONS

Although it is customary to speak loosely of gain and power in microwave circuits, these quantities can be defined in several different ways. The different definitions of gain are related to the concepts of *available* and *dissipated* power. These concepts are important in both linear and nonlinear circuits, although they are particularly important in nonlinear circuits, where a waveform may have components at many frequencies that may or may not be harmonically related.

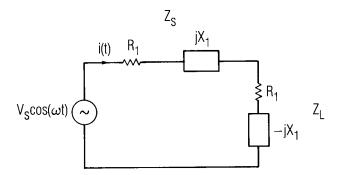

Available or transferable power is the maximum power that can be obtained from a source. The concept of available power is illustrated in Figure 1.6, in which a sinusoidal voltage source having a peak value  $V_s$  has an internal impedance of  $R_1 + jX_1$  (unless we state otherwise, all frequency-domain voltages and currents in this book are phasor quantities; thus, their magnitudes are equal to peak sinusoidal quantities, not RMS). The maximum power is obtained from this source if the load impedance equals the conjugate of the source impedance,  $Z_L = Z_s^* = R_1 - jX_1$ . Under these conditions,

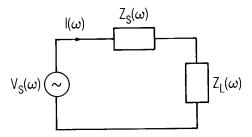

Figure 1.8 Unmatched circuit having a nonsinusoidal voltage-source excitation.

Figure 1.9 Unmatched circuit having a nonsinusoidal current-source excitation.

$$I = \frac{V_s}{2R_1} \tag{1.27}$$

where I is the peak value of the current, i(t). The power dissipated in the load,  $P_d$ , is

$$P_d = P_{av} = \frac{1}{2}I^2R_1 = \frac{1}{2}I^2Re\{Z_s\} = \frac{V_s^2}{8Re\{Z_s\}}$$

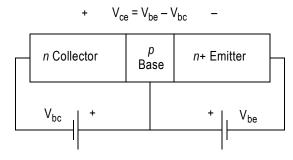

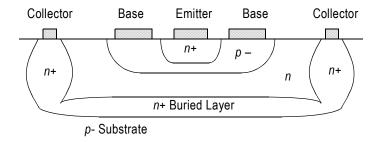

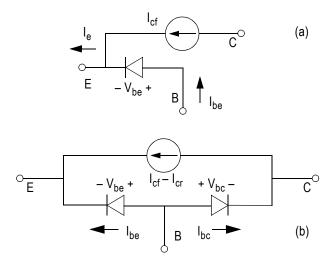

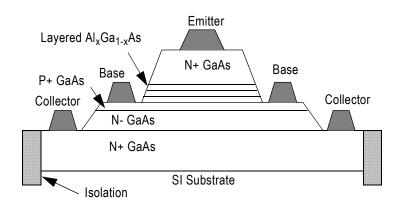

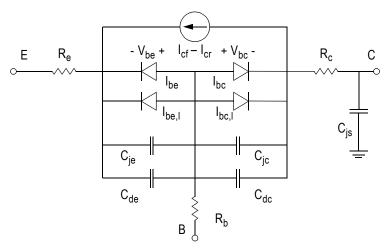

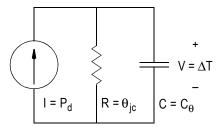

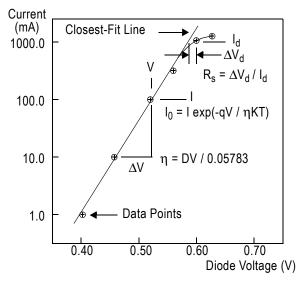

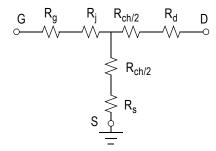

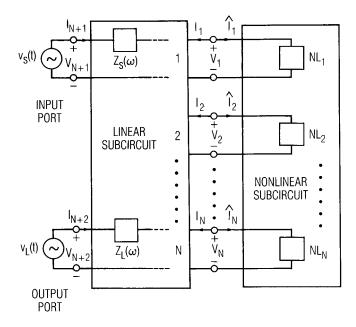

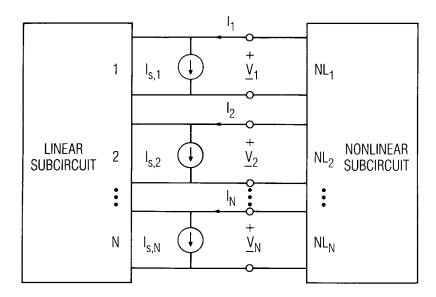

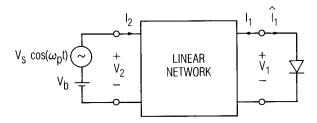

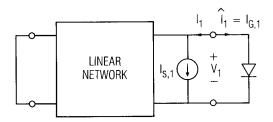

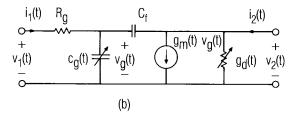

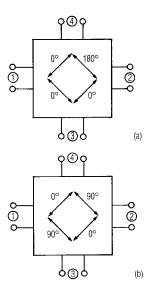

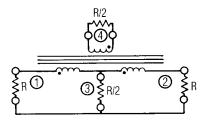

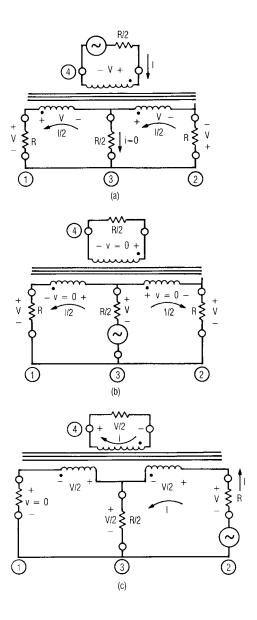

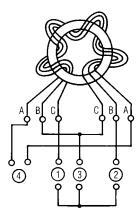

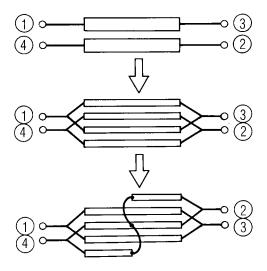

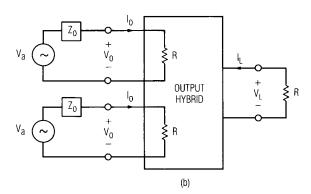

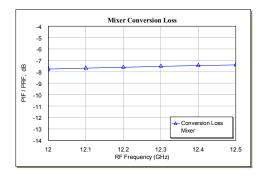

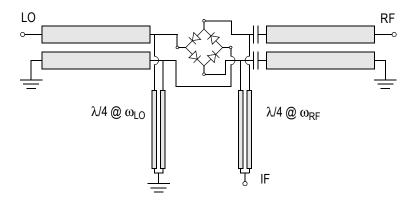

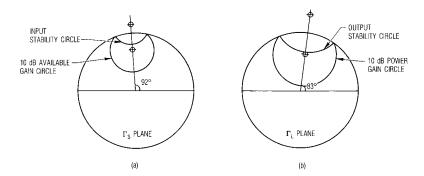

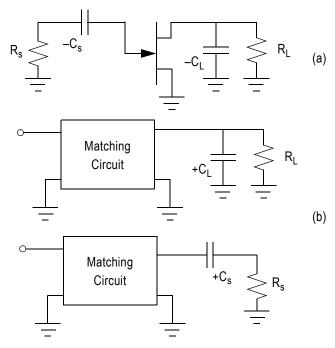

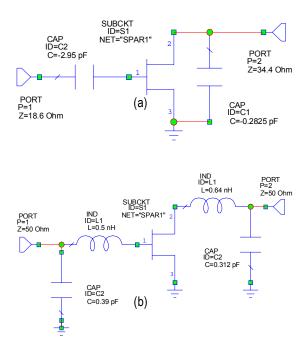

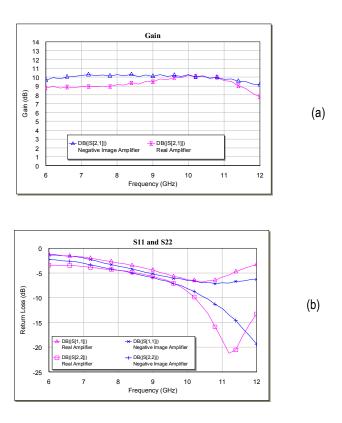

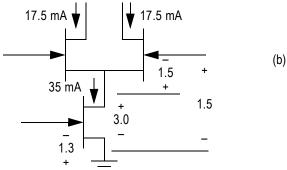

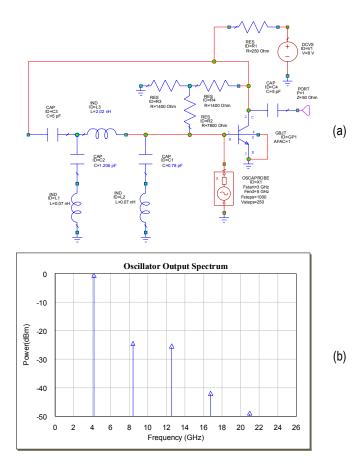

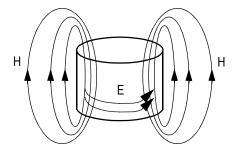

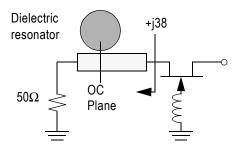

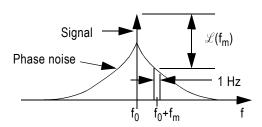

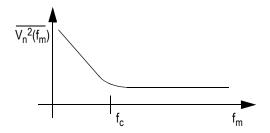

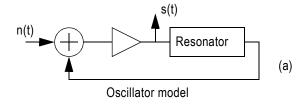

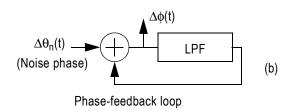

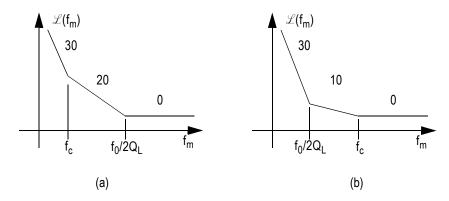

(1.28)