Philip Simpson

# FPGA Design

Best Practices for Team-based Design

### FPGA Design

Philip Simpson

### FPGA Design

Best Practices for Team-based Design

Philip Simpson Altera Corporation San Jose, CA 95134 USA Feilmidh@sbcglobal.net

ISBN 978-1-4419-6338-3 e-ISBN 978-1-4419-6339-0 DOI 10.1007/978-1-4419-6339-0 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010930598

© Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

© 2010 Altera Corporation

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat & Tm. Off. and Altera marks in and outside the U.S.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Preface**

In August of 2006, an engineering VP from one of Altera's customers approached Misha Burich, VP of Engineering at Altera, asking for help in reliably being able to predict the cost, schedule and quality of system designs reliant on FPGA designs.

At this time, I was responsible for defining the design flow requirements for the Altera design software and was tasked with investigating this further.

As I worked with the customer to understand what worked and what did not work reliably in their FPGA design process, I noted that this problem was not unique to this one customer. The characteristics of the problem are shared by many Corporations that implement designs in FPGAs. The Corporation has many design teams at different locations and the success of the FPGA projects vary between the teams. There is a wide range of design experience across the teams. There is no working process for sharing design blocks between engineering teams.

As I analyzed the data that I had received from hundreds of customer visits in the past, I noticed that design reuse among engineering teams was a challenge. I also noticed that many of the design teams at the same Companies and even within the same design team used different design methodologies.

Altera had recently solved this problem as part of its own FPGA design software and IP development process.

I worked with the top talent in Altera Engineering to develop a Best Practices Design methodology based upon Altera's experience and the techniques used by many customers successfully in FPGA design. The resulting methodology was presented and implemented at the customer, with great success.

Through the analysis of past customer data and feedback from customers over the last 3 years, it has become clear that this challenge exists broadly in the industry. The challenge is not specific to one specific FPGA vendor; it is an industry wide challenge.

As such, I have tuned the Best practices FPGA design methodology over the last 3 years and deployed it at several customers with great success.

This book captures the Best Practices FPGA design methodology and now makes it available to all design teams implementing system designs in FPGA devices.

San Jose, CA Philip Simpson

### **Contents**

| 1 | Best | Practi  | ces for Successful FPGA Design                   | J  |

|---|------|---------|--------------------------------------------------|----|

|   | 1.1  | Introd  | uction                                           | 1  |

| 2 | Pro  | iect Ma | nagement                                         | 5  |

|   | 2.1  |         | ole of Project Management                        |    |

|   |      | 2.1.1   |                                                  | 5  |

|   |      | 2.1.2   | •                                                | 6  |

|   |      | 2.1.3   | Schedule                                         | 6  |

| 3 | Desi | ign Spe | cification                                       | ç  |

|   | 3.1  |         | n Specification: Communication Is Key to Success | ç  |

|   |      | 3.1.1   | = -                                              | ç  |

|   |      |         | Functional Design Specification                  | 10 |

| 4 | Res  | ource S | coping                                           | 15 |

|   | 4.1  |         | uction                                           | 15 |

|   | 4.2  |         | eering Resources                                 | 15 |

|   | 4.3  |         | Party IP                                         | 16 |

|   | 4.4  |         | e Selection                                      | 16 |

|   |      | 4.4.1   | Silicon Specialty Features                       | 17 |

|   |      | 4.4.2   | Density                                          | 18 |

|   |      | 4.4.3   | Speed Requirements                               | 19 |

|   |      | 4.4.4   | Pin-Out                                          | 19 |

|   |      | 4.4.5   | Power                                            | 20 |

|   |      | 4.4.6   | Availability of IP                               | 20 |

|   |      | 4.4.7   | Availability of Silicon                          | 20 |

|   |      | 4.4.8   | Summary                                          | 21 |

| 5 | Desi | ign Env | rironment                                        | 23 |

|   | 5.1  | Introd  | uction                                           | 23 |

|   | 5.2  |         | ing Environment                                  | 23 |

|   | 5.3  |         | ction with Version Control Software              | 24 |

|   | 5.4  | Use of  | f a Problem Tracking System                      | 25 |

viii Contents

|   | 5.5 | A Regression Test System                              | 26 |

|---|-----|-------------------------------------------------------|----|

|   | 5.6 | When to Upgrade the Versions of the FPGA Design Tools | 26 |

|   | 5.7 | Common Tools in the FPGA Design Environment           | 27 |

| 6 | Boa | rd Design                                             | 29 |

|   | 6.1 | Challenges that FPGAs Create for Board Design         | 29 |

|   | 6.2 | Engineering Roles and Responsibilities                | 30 |

|   |     | 6.2.1 FPGA Engineers                                  | 30 |

|   |     | 6.2.2 PCB Design Engineer                             | 31 |

|   |     | 6.2.3 Signal Integrity Engineer                       | 32 |

|   | 6.3 | Power and Thermal Considerations                      | 33 |

|   |     | 6.3.1 Filtering Power Supply Noise                    | 33 |

|   |     | 6.3.2 Power Distribution                              | 33 |

|   | 6.4 | Signal Integrity                                      | 34 |

|   |     | 6.4.1 Types of Signal Integrity Problems              | 34 |

|   |     | 6.4.2 Electromagnetic Interference                    | 35 |

|   | 6.5 | Design Flows for Creating the FPGA Pinout             | 36 |

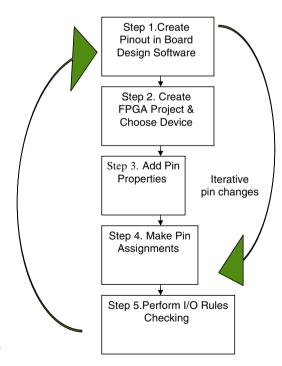

|   |     | 6.5.1 User Flow 1: FPGA Designer Driven               | 36 |

|   |     | 6.5.2 User Flow 2                                     | 38 |

|   |     | 6.5.3 How Do FPGA and Board Engineers Communicate     |    |

|   |     | Pin Changes?                                          | 40 |

|   | 6.6 | Board Design Check List for a Successful FPGA Pin-Out | 40 |

| 7 | Pow | ver and Thermal Analysis                              | 41 |

|   | 7.1 | Introduction                                          | 41 |

|   | 7.2 | Power Basics                                          | 42 |

|   |     | 7.2.1 Static Power                                    | 42 |

|   |     | 7.2.2 Dynamic Power                                   | 42 |

|   |     | 7.2.3 I/O power                                       | 42 |

|   |     | 7.2.4 Inrush Current                                  | 43 |

|   |     | 7.2.5 Configuration Power                             | 43 |

|   | 7.3 | Key Factors in Accurate Power Estimation              | 43 |

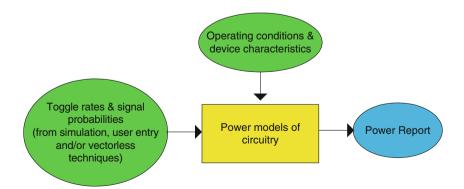

|   |     | 7.3.1 Accurate Power Models of the FPGA Circuitry     | 44 |

|   |     | 7.3.2 Accurate Toggle Rate Data on Each Signal        | 44 |

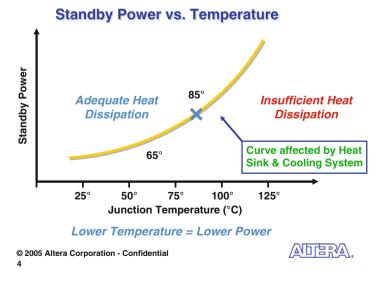

|   |     | 7.3.3 Accurate Operating Conditions                   | 45 |

|   |     | 7.3.4 Resource Utilization                            | 46 |

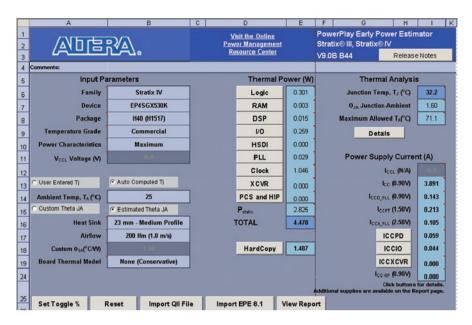

|   | 7.4 | Power Estimation Early in the Design Cycle            |    |

|   |     | (Power Supply Planning)                               | 46 |

|   | 7.5 | Simulation Based Power Estimation                     |    |

|   |     | (Design Power Verification)                           | 47 |

|   |     | 7.5.1 Partial Simulations                             | 50 |

|   | 7.6 |                                                       | 50 |

Contents ix

| 8  | RTL   | <b>Design</b>                                     |

|----|-------|---------------------------------------------------|

|    | 8.1   | Introduction                                      |

|    | 8.2   | Common Terms and Terminology                      |

|    | 8.3   | Recommendations for Engineers with an ASIC        |

|    |       | Design Background                                 |

|    | 8.4   | Recommended FPGA Design Guidelines                |

|    |       | 8.4.1 Synchronous Versus Asynchronous             |

|    |       | 8.4.2 Global Signals                              |

|    |       | 8.4.3 Dedicated Hardware Blocks                   |

|    |       | 8.4.4 Use of Low-Level Design Primitives          |

|    |       | 8.4.5 Managing Metastability                      |

|    | 8.5   | Writing Effective HDL                             |

|    |       | 8.5.1 What's the Best Language                    |

|    |       | 8.5.2 Good Design Practices 59                    |

|    |       | 8.5.3 HDL for Synthesis                           |

|    | 8.6   | Analyzing the RTL Design                          |

|    |       | 8.6.1 Synthesis Reports                           |

|    |       | 8.6.2 Messages                                    |

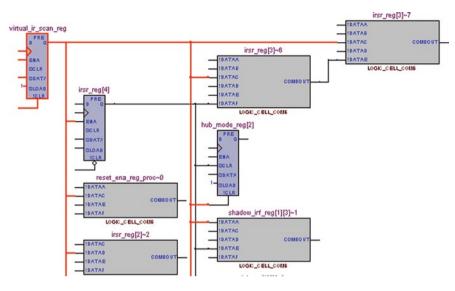

|    |       | 8.6.3 Block Diagram View                          |

|    | 8.7   | Recommended Best Practices for RTL Design         |

| 0  | TD    | ID t D                                            |

| 9  |       | nd Design Reuse                                   |

|    | 9.1   | Introduction 79                                   |

|    | 9.2   | The Need for IP Reuse 79                          |

|    |       | 9.2.1 Benefits of IP Reuse                        |

|    |       | 9.2.2 Challenges in Developing a Design           |

|    | 0.2   | Reuse Methodology                                 |

|    | 9.3   | Make Versus Buy                                   |

|    | 9.4   | Architecting Reusable IP                          |

|    |       | 9.4.1 Specification 83                            |

|    |       | 9.4.2 Implementation Methods 83                   |

|    | 0.5   | 9.4.3 Use of Standard Interfaces                  |

|    | 9.5   | Packaging of IP 86                                |

|    |       | 9.5.1 Documentation                               |

|    |       | 9.5.2 User Interface 87                           |

|    |       | 9.5.3 Compatibility with System Integration Tools |

|    | 0.6   | 9.5.4 IP Security                                 |

|    | 9.6   | IP Reuse Checklist 90                             |

| 10 | The 1 | Hardware to Software Interface91                  |

| -  | 10.1  | Software Interface 91                             |

|    | 10.2  | Definition of Register Address Map                |

|    | 10.3  | Use of the Register Address Map                   |

|    |       | 10.3.1 IP Selection                               |

|    |       | 10.3.2 Software Engineers Interface 92            |

x Contents

|    |       | 10.3.3     | RTL Engineers Interface                           | 92  |

|----|-------|------------|---------------------------------------------------|-----|

|    |       | 10.3.4     | Verification Interface                            | 93  |

|    |       | 10.3.5     | Documentation                                     | 93  |

|    | 10.4  | Summar     | y                                                 | 94  |

| 11 | Funct | ional Veri | fication                                          | 95  |

|    | 11.1  |            | tion                                              | 95  |

|    | 11.2  |            | es of Functional Verification                     | 95  |

|    | 11.3  |            | of Verification Concepts                          | 96  |

|    | 11.4  |            | sus Gate Level Simulation                         | 97  |

|    | 11.5  |            | ion Methodology                                   | 97  |

|    | 11.6  |            | omplexity                                         | 98  |

|    |       | 11.6.1     | Modularize Your Design and Your Tests             | 98  |

|    |       | 11.6.2     | Plan for Expected Operation                       | 98  |

|    |       | 11.6.3     | Plan for the Unexpected                           | 98  |

|    | 11.7  | Function   | al Coverage                                       | 99  |

|    |       | 11.7.1     | Directed Testing                                  | 100 |

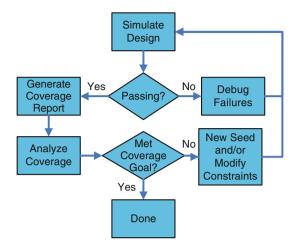

|    |       | 11.7.2     | Random Dynamic Simulation                         | 100 |

|    |       | 11.7.3     | Constrained Random Tests                          | 100 |

|    |       | 11.7.4     | Use of System Verilog for Design and Verification | 100 |

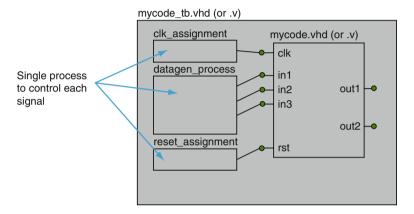

|    |       | 11.7.5     | General Testbench Methods                         | 101 |

|    |       | 11.7.6     | Self Verifying Testbenches                        | 102 |

|    |       | 11.7.7     | Formal Equivalency Checking                       | 103 |

|    | 11.8  | Code Co    | verage                                            | 104 |

|    | 11.9  | QA Testi   | ng                                                | 104 |

|    |       | 11.9.1     | Functional Regression Testing                     | 104 |

|    |       | 11.9.2     | GUI Testing for Reusable IP                       | 105 |

|    | 11.10 | Hardwar    | e Interoperability Tests                          | 105 |

|    | 11.11 |            | e/Software Co-Verification                        | 106 |

|    |       | 11.11.1    | Getting to Silicon Fast                           | 106 |

|    | 11.12 | Functiona  | l Verification Checklist                          | 106 |

| 12 | Timin | g Closure  |                                                   | 107 |

|    | 12.1  | _          | Closure Challenges                                | 107 |

|    | 12.2  |            | ortance of Timing Assignments and Timing Analysis | 108 |

|    |       | 12.2.1     | Background                                        | 108 |

|    |       | 12.2.2     |                                                   | 109 |

|    | 12.3  | A Metho    | dology for Successful Timing Closure              | 115 |

|    |       | 12.3.1     | Family and Device Assignments                     | 115 |

|    |       | 12.3.2     | Design Planning                                   | 116 |

|    |       | 12.3.3     | Early Timing Estimation                           | 121 |

|    |       | 12.3.4     | CAD Tool Settings                                 | 122 |

|    | 12.4  | Commor     | Timing Closure Issues                             | 129 |

|    |       | 12.4.1     | Missing Timing Constraints                        | 130 |

|    |       | 12.4.2     | Conflicting Timing Constraints                    | 130 |

Contents xi

|     |         | 12.4.3   | High Fan-Out Registers                     | 130 |

|-----|---------|----------|--------------------------------------------|-----|

|     |         | 12.4.4   | Missing Timing by a Small Margin           | 131 |

|     |         | 12.4.5   | Restrictive Location Constraints           | 131 |

|     |         | 12.4.6   | Long Compile Times                         | 131 |

|     | 12.5    | Design   | Planning, Implementation, Optimization and |     |

|     |         |          | Closure Checklist                          | 132 |

| 13  | In-Sy   | stem De  | bug                                        | 133 |

|     | 13.1    | In-Syste | em Debug Challenges                        | 133 |

|     | 13.2    | Plannin  | ıg                                         | 134 |

|     | 13.3    | Technic  | ques                                       | 134 |

|     |         | 13.3.1   | Use of Pins for Debug                      | 134 |

|     |         | 13.3.2   | Internal Logic Analyzer                    | 135 |

|     |         | 13.3.3   | Use of Debug Logic                         | 138 |

|     |         | 13.3.4   | External Logic Analyzer                    | 139 |

|     |         | 13.3.5   | Editing Memory Contents                    | 139 |

|     |         | 13.3.6   | Use of a Soft Processor for Debug          | 140 |

|     | 13.4    | Use Sce  | enarios                                    | 140 |

|     |         | 13.4.1   | Power-Up Debug                             | 140 |

|     |         | 13.4.2   | Debug of Transceiver Interfaces            | 141 |

|     |         | 13.4.3   | Reporting of System Performance            | 141 |

|     |         | 13.4.4   | Debug of Soft Processors                   | 142 |

|     |         | 13.4.5   | Device Programming Issues                  | 143 |

|     | 13.5    | In-Syst  | em Debug Checklist                         | 144 |

| 14  | Desig   | n Sign-( | Off                                        | 145 |

|     | 14.1    | Sign-O   | ff Process                                 | 145 |

|     | 14.2    | After S  | ign-Off                                    | 145 |

| Bib | liograj | ohy      |                                            | 147 |

| Ind | ex      |          |                                            | 149 |

### **List of Figures**

| Fig. 1.1 | Three steps to successful FPGA development                               | 2  |

|----------|--------------------------------------------------------------------------|----|

| Fig. 1.2 | Recommended best practices design methodology for successful FPGA design | 3  |

| Fig. 2.1 | Percentage complete dilemma                                              | 7  |

| 116. 2.1 | Tereonage comprese anomina                                               | ,  |

| Fig. 3.1 | Sample revision control page                                             | 11 |

| Fig. 6.1 | Example .csv file that interfaces between board design                   |    |

|          | SW and FPGA SW                                                           | 32 |

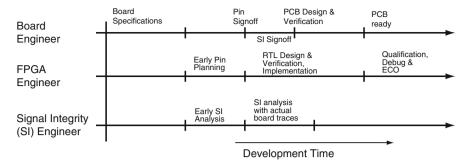

| Fig. 6.2 | Design cycle diagram detailing engineering                               |    |

|          | discipline involvement                                                   | 33 |

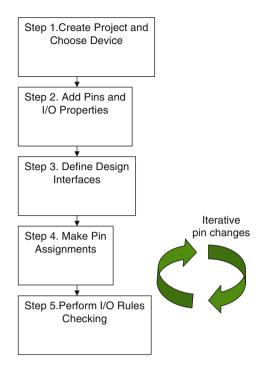

| Fig. 6.3 | FPGA designer driven flow for creating the FPGA pin-out                  | 37 |

| Fig. 6.4 | Board designer driven flow                                               | 39 |

| Fig. 7.1 | Key elements in accurate power estimation                                | 43 |

| Fig. 7.2 | Graph of standby current versus temperature                              | 45 |

| Fig. 7.3 | Sample power estimation spreadsheet for                                  |    |

|          | the Altera Stratix IV GX family                                          | 47 |

| Fig. 7.4 | Probability of nodes toggling                                            | 49 |

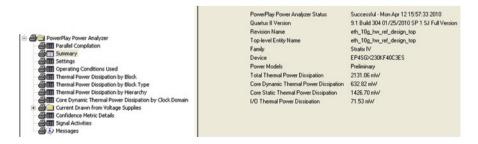

| Fig. 7.5 | Sample power estimation report from                                      |    |

|          | Quartus II PowerPlay Estimator                                           | 49 |

| Fig. 7.6 | Best practices for power estimation                                      | 50 |

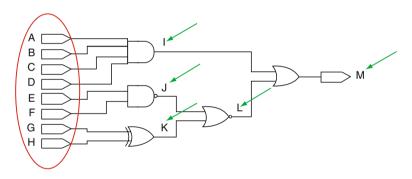

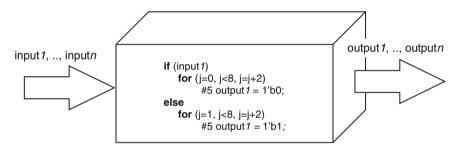

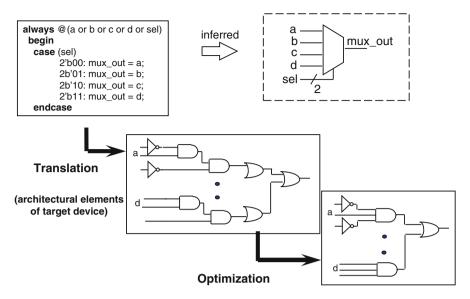

| Fig. 8.1 | Behavioral modeling                                                      | 52 |

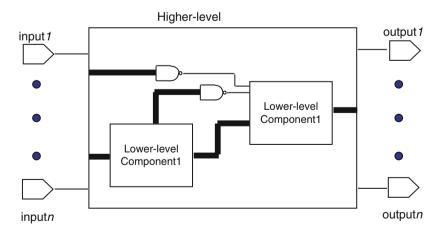

| Fig. 8.2 | Structural modeling                                                      | 52 |

| Fig. 8.3 | Synthesis                                                                | 53 |

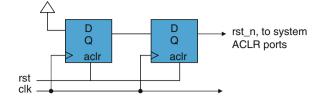

| Fig. 8.4 | Synchronizer for an asynchronous reset                                   | 55 |

| Fig. 8.5 | Instantiation versus inferencing                                         | 56 |

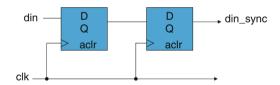

| Fig. 8.6 | Two-register synchronizer                                                | 57 |

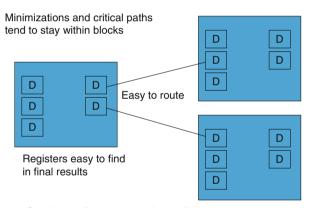

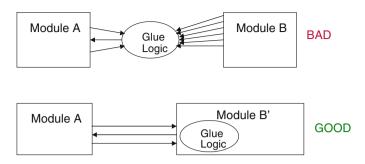

| Fig. 8.7 | Good design partitioning                                                 | 61 |

| Fig. 8.8 | Example bad and good partition                                           | 62 |

| Fig. 8.9 | Sample code for dealing with tristates at partition boundaries           | 62 |

|          |                                                                          |    |

xiv List of Figures

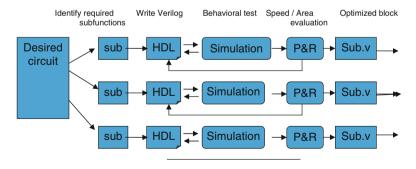

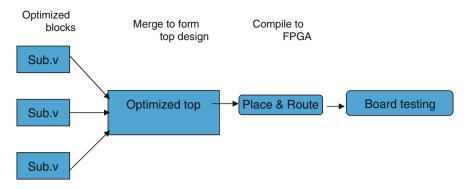

| Fig. 8.10 | Divide and conquer approach to RTL design              | 62  |

|-----------|--------------------------------------------------------|-----|

| Fig. 8.11 | Combine sub-blocks to create an optimized design block | 63  |

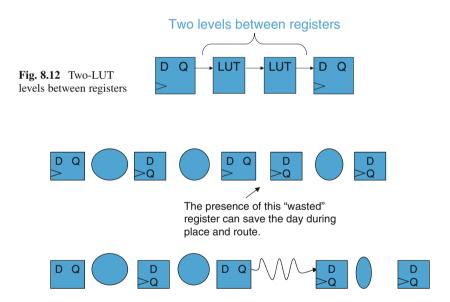

| Fig. 8.12 | Two-LUT levels between registers                       | 67  |

| Fig. 8.13 | Use of pipeline stages to break up routing delays      | 67  |

| Fig. 8.14 | New data on simultaneous read/write                    | 69  |

| Fig. 8.15 | Coding style that will infer a RAM that returns        |     |

| <b>6</b>  | the OLD data on a simultaneous read/write              | 69  |

| Fig. 8.16 | Initialize the RAM contents to all 1 s                 | 70  |

| Fig. 8.17 | Inferencing of a ROM                                   | 70  |

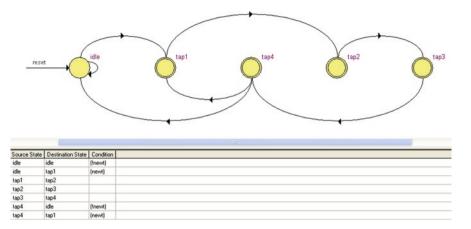

| Fig. 8.18 | Finite state machine                                   | 70  |

| Fig. 8.19 | Use of enumerated types in VHDL for state              |     |

| 118, 011  | machine inferencing                                    | 71  |

| Fig. 8.20 | Verilog FSM                                            | 71  |

| Fig. 8.21 | State machine encoding styles                          | 71  |

| Fig. 8.22 | Multiply-accumulate operation                          | 73  |

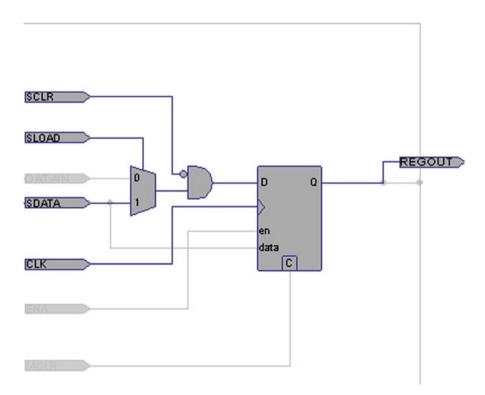

| Fig. 8.23 | Verilog example of a register                          | 73  |

| Fig. 8.24 | Register in VHDL                                       | 73  |

| Fig. 8.25 | Synthesis priority of secondary control                | , 5 |

| 116.0.20  | signals for registers                                  | 74  |

| Fig. 8.26 | Multiplexer tree                                       | 74  |

| Fig. 8.27 | N:1 multiplexer                                        | 75  |

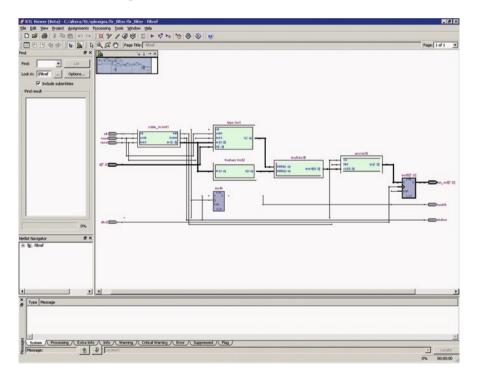

| Fig. 8.28 | Quartus II RTL viewer                                  | 77  |

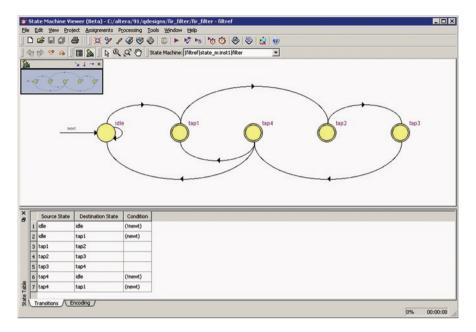

| Fig. 8.29 | Quartus II state machine viewer                        | 78  |

| 116.0.2   | Quartus 11 state inacimie (16 voi                      | , 0 |

| Fig. 9.1  | Example detailing the use of parameters in a           |     |

| 8         | Verilog source file                                    | 84  |

| Fig. 9.2  | Sample GUI for IP demonstrated by the                  | ٠.  |

| 8         | Quartus II Component Editor                            | 88  |

|           | Quartur is compositive Zurior                          |     |

| Fig. 10.1 | Sample from Header file generated by the               |     |

| 8         | Altera SOPC Builder tool                               | 92  |

|           |                                                        |     |

| Fig. 11.1 | Constrained random test flow                           | 101 |

| Fig. 11.2 | Simple testbench that requires manual checking         | 102 |

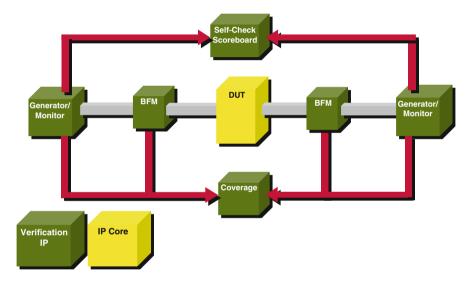

| Fig. 11.3 | Example diagram of a self-checking testbench           | 103 |

| Fig. 11.4 | Verification system architecture                       | 103 |

| 8         | ,                                                      |     |

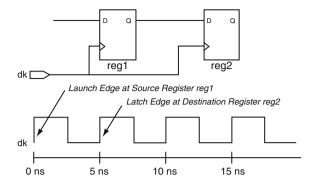

| Fig. 12.1 | Launch and latch edge diagram                          | 110 |

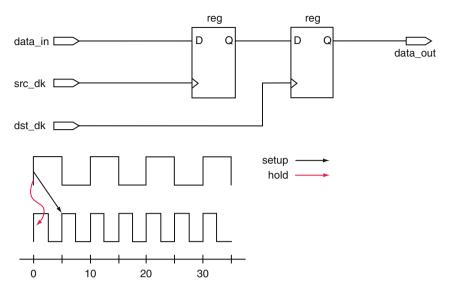

| Fig. 12.2 | tsu and th diagram                                     | 111 |

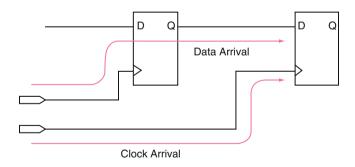

| Fig. 12.3 | Clock arrival and data arrival diagram                 | 111 |

| Fig. 12.4 | Multi-cycle path                                       | 112 |

| Fig. 12.5 | Input delay                                            | 113 |

| Fig. 12.6 | Output delay                                           | 113 |

| Fig. 12.7 | Clock uncertainty                                      | 115 |

| Fig. 12.8 | Bottom-up design flow                                  | 118 |

List of Figures xv

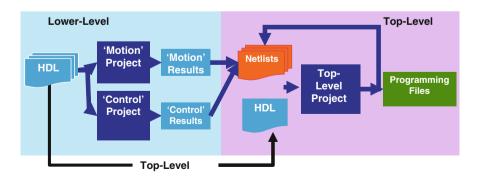

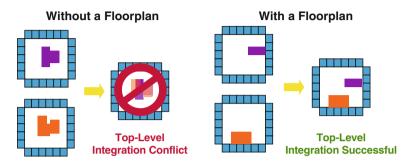

| Fig. 12.9  | Integration of modules in the top-level design         | 119 |

|------------|--------------------------------------------------------|-----|

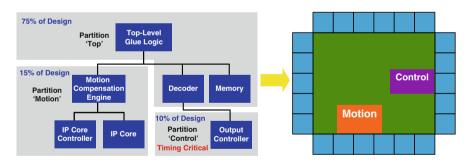

| Fig. 12.10 | Example design partitioned for incremental compilation | 119 |

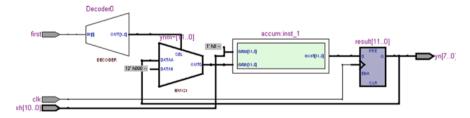

| Fig. 12.11 | Example of the RTL viewer in the Quartus II software   | 125 |

| Fig. 12.12 | Example view of a FSM from the Quartus II RTL viewer   | 126 |

| Fig. 12.13 | Critical Path View in Quartus II                       |     |

|            | technology map viewer                                  | 127 |

| Fig. 12.14 | The Quartus II chip planner detailing the              |     |

|            | Stratix IV ALM architecture                            | 127 |

### **Chapter 1 Best Practices for Successful FPGA Design**

#### 1.1 Introduction

This book which describes the Best Practices for successful FPGA design is the result of meetings with hundreds of customers on the challenges facing each of their FPGA design teams. By gaining an understanding into their design environments, processes, what works, what does not work, I have been able to identify the areas of concern in implementing System designs. More importantly, it has enabled me to document a recommended methodology that provides guidance in applying a best practices design methodology to overcome the challenges.

This material has a strong focus on design teams that are across sites. The goal being to increase the productivity of FPGA design teams by establishing a common methodology across design teams; enabling the exchange of design blocks across teams.

Best Practices establishes a roadmap to predictability for implementing system designs in a FPGA.

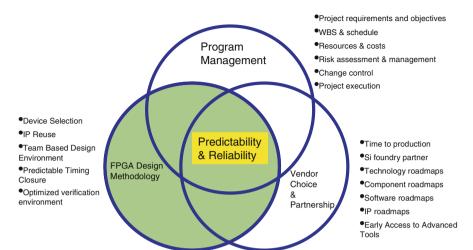

The three steps (Fig. 1.1) to predictable results are:

- 1. Proper project planning and scoping

- 2. Choosing the right FPGA device to ensure that the right technology is available for today's and tomorrow's projects

- 3. Following the best practices for FPGA design development in order to shorten the design cycle and to ensure that your designs are complete on schedule and that the design blocks can be re-used on future projects with minimal effort

All three elements need work together smoothly to guarantee a successful FPGA design.

The choice of vendor should be a long-term partnership between the Companies. By sharing roadmaps and jointly managing existing projects, you can ensure that not only is the current project a success but provide the right solutions on time for future projects. A process of fine tuning based on experience working together to guarantee success on projects.

These two topics are touched upon briefly in the Best Practices for Successful FPGA Design methodology.

#### **Key Elements to Successful FPGA Design**

Fig. 1.1 Three steps to successful FPGA development

The third topic is the FPGA design methodology.

This is the main focus of the best practices methodology. This covers the complete FPGA design flow from the basics to advanced techniques. This methodology is FPGA vendor independent in that the topics and recommendations are good practices that apply to the design of any FPGAs. While most of the material is generic, it does contain references to features in the Altera design tools that reinforce the recommended best practices.

The diagram that is shown in Fig. 1.2 shows the outline of the best practices design methodology.

Each of the blocks in the diagram is represented by chapters in this book, with an additional chapter on power. Power is its own chapter as it spans many of the other areas of the design methodology. The topics of Board Layout, RTL Design, IP Reuse, Functional Verification and Timing Closure tend to be the areas where design teams have different design methodologies and engineers need guidance on achieving consistent results and shortening the design cycle.

Many of the challenges that are faced in FPGA design are not unique to FPGA design but are common challenges in system design. FPGA devices themselves do provide unique challenges and opportunities compared to ASIC designs. The increase in capability of FPGA devices has resulted in much more complex designs targeting FPGAs and a natural migration of ASIC designers to FPGA design. This has resulted in many design teams migrating ASIC design principles to FPGA designs. In general, this has been a benefit to the FPGA design flow; however it needs to be balanced with the benefits that FPGAs bring to the design flow. The programmable nature of FPGAs opens the door to performing more verification

1.1 Introduction 3

#### **Proiect** Specification Management Resource Scoping SW **Board Design RTL** ΙP Development **Functional** Verification Timing Design Environment In-System Debug Infrastructure Design Sign-off

#### **Recommended Design Methodology**

Fig. 1.2 Recommended best practices design methodology for successful FPGA design

in-system. When used correctly, this can greatly speed-up the verification cycle, however when abused it can lengthen the design cycle. The configurable nature of I/Os provides challenges that do not exist in ASIC design. The tools that are used from the EDA industry are also different for FPGAs than for ASICs, in both functionality and cost.

This book will help you adopt the best design methodology to meet your requirements.

While it is recommended that you read the book in its entirety, you can also focus on the individual chapters of the book that target the areas of the design flow that is causing the biggest challenge to your design team.

Acknowledgements Misha Burich for providing the idea for Best Practices. Brian Holley and Rich Catizone for driving the idea at their customer base and providing a constant source of feedback. Chris Balough for encouragement on creating this book. Thomas Sears – Providing access to his development teams, without whom this would not have been possible. YK Ning, Jeff Fox, Ajay Jagtiani, Alex Grbic, Joshua Walstrom, Oliver Tan & Joshua Fender for contributing material to the original presentations on Best Practices. The many customers who have contributed to the material by describing their design environments and the challenges that they have faced in completing their system designs in FPGA devices. My wife Jill and daughter Kayla for their patience and support through the process of gathering data and writing the book.

### Chapter 2 Project Management

#### 2.1 The Role of Project Management

The scope of project management is to deliver the right features, on-time and within budget. As such there are three dimensions:

- 1. Features

- 2. Development time

- 3. Resources

The project manager needs to find the right balance of these three dimensions to meet the goals of the project.

There are numerous books and training classes on project management. This chapter provides a brief overview of the elements of project management. It is recommended that you attend formal project management training.

#### 2.1.1 Project Management Phases

Every project can be broken into three project management phases.

- 1. The planning phase. This is establishing the feature list, creating the project plan and establishing the resource pools and budget.

- 2. The tracking phase. This involves holding monthly feature reviews, weekly plan updates, reviewing the budget and staffing levels and reviewing any Engineering Change Orders.

- 3. The wrap-up Phase. This involves project retrospectives, data mining and process improvement review and action plan.

#### 2.1.2 Estimating a Project Duration

Estimating the overall project delivery target is best done with the following steps.

- 1. Select one of the latest successfully major completed projects.

- 2. Create a macro model. This involves identifying the major project phases for specification, designing and verification. Extract the exact duration of the phases and any overlap.

- 3. Set the overall process improvement target. An example would be stating that I want to implement a project of similar complexity 10% faster.

- 4. Define project complexity metrics such as design characteristics and resource utilization. Design characteristics can include the number of pages of specification, the number of FPGA resources, the number of lines of RTL, design performance technical complexity.

- 5. Derive the derating factor k.

- 6. Scale the upcoming project by the derating factor.

- 7. Evaluate the project with good judgment and make the appropriate adjustments.

#### 2.1.3 Schedule

The project schedule should be updated regularly. It is recommended that it is updated at least once a week.

Any schedule update meetings should be kept brief and should only focus on collecting the status information. This includes information on whether a task has started, is an activity complete, how long will a task take to complete, and any user task information that determines the level of completeness of a task.

The update meetings should also be used to estimate when a task is expected to be complete. The project manager must respect the duration estimates from the resources performing a task but should question any estimates that appear to be wildly wrong.

#### 2.1.3.1 Weekly Schedule Analysis

The project manager needs to rigorously analyze the project schedule on a weekly basis. There are ten main tasks involved in this process.

- 1. Analyzing and scrutinizing the critical paths.

- 2. Reviewing the planned tasks for the coming week.

- 3. Discussing and agreeing on the task priorities with the rest of the review team.

- 4. Identifying a plan to accelerate the critical path.

- 5. Identifying other at risk paths that are just behind the critical path.

- 6. Checking the load on the resources assigned to the critical path.

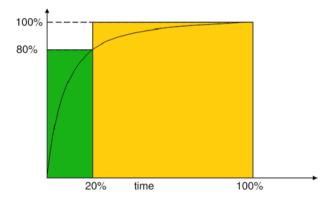

Fig. 2.1 Percentage complete dilemma

- 7. Confirming the availability of resources with the managers.

- 8. Determining the part of the project plan that needs more work.

- 9. Capturing action items.

- 10. Performing task refinements.

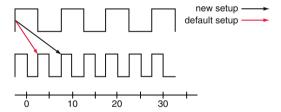

It is critical that the project manager does not get fooled by the percentage complete. It is a non-linear function and is not useful in estimating the remaining task duration (Fig. 2.1).

#### 2.1.3.2 Pro-active Project Management

It requires an extreme degree of pro-active behavior to deliver a project on time. Be sure to dedicate enough management bandwidth to the project.

Due to the dynamic circumstances of design projects, it requires constant management attention with weekly rigorous project schedule updates.

The complexity of the project require the right tools to facilitate the decision making process. The identification and management of the critical path simplifies the priority setting.

# **Chapter 3 Design Specification**

#### 3.1 Design Specification: Communication Is Key to Success

Having a complete and detailed specification early in a project will prevent false starts and reduce the likelihood of Engineering Change Orders (ECOs) late in the project. Late changes to the design specification can dramatically increase the cost of a project both in terms of the project schedule and the cost of the FPGA. The latter occurring as significant changes may result in the need for a larger FPGA device.

The purpose of a specification is to accurately and clearly communicate information.

Another way of saying this is that specifications are a means to convey information between teams/people. Without a thorough specification, which has been approved by all impacted parties, a project is prone to delays and late changes in the requirements; all of which lead to longer project cycles and higher project cost. A key point in this statement is "agreed upon specification". This implies that a process is in place for the review of the specification.

A fully agreed upon specification ensures alignment between the different teams working on the project. This ensures that the delivered product conforms to the functional specifications and meets the customer requirements. This in turn facilitates accurate estimation of development cost, resource & project schedule. A solid specification enables consistent project tracking, which will ultimately produce a high quality product release. The specification also serves as a reference for the creation of documentation and collateral to be delivered with, or to support the product. All specifications should clearly identify changes that have been made to the specification. In addition, the specification should be stored under version control software.

Specifications are required at different stages of the FPGA design from definition through the development process.

#### 3.1.1 High Level Functional Specification

The high level functional specification is created and owned by the systems engineering team. This document describes the basic functionality of the FPGA design including

the required interaction with the software interface and the interfaces between the FPGA and other devices on the board. This document should be officially reviewed with the FPGA design team Manager and the Software engineering manager. After the review, the document should be updated to reflect the recommend changes and to answer any of the issues raised during the review process. This process is iterative until all issues have been resolved and the FPGA design team understands and agrees upon the requirements.

One of the challenges in creating the high level functional specification is successfully describing the functionality in understandable English. Let's be honest here; most Engineers are strong in mathematics and science but will never be the next John Steinbeck.

Executable specifications help resolve this issue. Executable specifications are abstract models of the system that describe the functionality of the end system. It is essentially a virtual prototype of the system. Most executable specifications are created in one of the flavors of "C" (C, C++, System). These languages are good for modeling the desired functionality but do not cover key features such as timing, power and size of design. These need to be covered in an accompanying high level specification to the executable specification. The virtual prototype at this stage is the system model and the testbench which is part of the executable specification. This executable specification can be used throughout the development process to check that the detailed implementation is meeting the requirements of the executable specification.

Not all Companies are using executable specifications as part of the FPGA design process, but its use is becoming more common as more complex systems are being implemented in FPGA devices.

#### 3.1.2 Functional Design Specification

The team that is creating the FPGA design should create a detailed design specification that represents the needs of the high level functional specification. The owner of this specification is the FPGA engineering team. This specification should be reviewed and approved by the FPGA design team, their management and with representation from the systems engineering and software engineering teams. This should finalize the specification for the functionality of the FPGA design and detail the interfaces with the rest of the system including software.

It is critical to agree upon the details of the interfaces to the FPGA with the appropriate development teams that will use these interfaces.

Take for example, the H/W to S/W interface for a design where an A/D converter feeds the FPGA. The FPGA in turn feeds data to a microprocessor. The FPGA requirements specification must cover the interface to the A/D and be designed to avoid any functional failures, even under corner case conditions. Failure to do so can result in functional failures not showing up until testing the design in system. Board tests could show the FPGA passing junk data to the S/W interfaces. The S/W engineers

will likely not know how to interpret or debug this issue. This can result in extended board test time and under worst case scenario a redesign of either the software and/ or the FPGA design; ultimately this will result in a delay to the schedule.

#### 3.1.2.1 Functional Specification Outline

In this section, we will detail the minimum set of requirements that need to be included in the functional specification.

- 1. Revision history. A sample revision control page is shown in Fig. 3.1. This includes the date of the changes, the author of the changes and the approval of the changes.

- Review minutes. This should include details on all review meetings on the specification. The minutes should include the meeting date and location, attendees, minutes and the action items that need to be resolved to gain approval of the specification.

- 3. Table of contents.

- 4. Feature overview. The feature overview should provide context of the system in which the feature will be provided. If the feature is a subsystem in the end FPGA system design, this section should describe where it fits in the overall system and its purpose, i.e. the problem it solves. The feature overview should also include a high level overview of its required functionality.

- 5. Source references. This section should describe the driver of the feature request, e.g. High Level Functional Specification, Software Interface Functional Requirements, etc.

- 6. Glossary. The glossary should describe any industry standard terms and acronyms that are used in the document. More importantly, it should also do this for any internal Company terminology used in the document. It is amazing how much time is wasted and confusion caused due to the use of internal Company terminology. Many new employees or employees from other groups are often embarrassed to admit that they do not understand the "code" words in review meetings, resulting in confusion, delays in decision and often the stifling of creativity.

#### **Revision History**

| Version | Author   | Date    | Changes                                                                             |

|---------|----------|---------|-------------------------------------------------------------------------------------|

| 0.9     | psimpson | 4-26-09 | Initial revision                                                                    |

| 1.0     | psimpson | 5-11-09 | Added timing details to CODEC                                                       |

| 1.1     | aclarke  | 5-30-09 | Modified register map based upon review with SW Engineering on May 28, 2009.        |

| 1.2     | jjones   | 6-3-09  | Adding a section to describe the interface to host processor.                       |

| 1.3     | psimpson | 6-9-09  | Updated host processor interface after second review with SW Engineering on June 4. |

Fig. 3.1 Sample revision control page

- 7. Detailed feature description. This is really the meat of the document. This section should include descriptions of any of the algorithms used, details on the architecture of the design and the interface with other parts of the design or system.

- 8. Test plan. The document should refer to the test plan, or at a minimum state the need for a test plan and be updated when the test plan exists.

- 9. References. In this section the document should refer to all supporting documents that should be read to understand the functional specification.

Following the creation of the detailed FPGA design specification, the engineering team will create a number of specifications for internal review within the engineering department. These include the Functional Test Plan and QA Test Plan. Each engineer that is assigned to the project will create an engineering plan and functional test plan for the portion of the design that they will be implementing. This should be reviewed within engineering against the overall functional plan. This ensures that it meets the overall requirements of the FPGA design.

#### 3.1.2.2 Test Specification Outline

- 1. Revision history. A sample revision control page is shown in Fig. 3.1. This includes the date of the changes, the author of the changes and the approval of the changes.

- Review minutes. This should include details on all review meetings on the specification. The minutes should include the meeting date and location, attendees, minutes and the action items that need to be resolved to gain approval of the specification.

- 3. Table of contents.

- 4. Scope. This will provide an overview of what specific features this test plan will cover. If test coverage overlaps with the testing of any subsystems, it should detail what will be covered in this test plan and refer to the other test plans.

- 5. Test requirements. This should detail any special hardware, software, EDA tools that are required to complete the testing. As part of this it should include any special set-up requirements.

- 6. Test strategy. This includes the pass/failure criteria. Do the test results require cross-verification with any other sub-systems. Will existing tests be re-used or modified to meet the needs of this test plan. Will the tests be automated and if so, how will the tests be automated. How will the tests be run. An example of this would be an automated regtest that is run each night, or manual testing to verify that the graphics appear correctly on the screen when run on a development board.

- 7. Automation plan. It is desirable to automate as much of the testing as possible. This section will describe how to automate the test.

- 8. Running the tests. What is the expected runtime of the tests. If the test is not automated, what is the expected time for the tests to be performed manually.

- 9. Test documentation. This section should include descriptions of the test cases. As standard practice, the test infrastructure should be set-up to isolate each test.

Thus each test case should have its own test directory. The documentation should detail how to access the results from the regression tests database. This assumes that a regression tests system has been established. Not establishing such a system is setting a project up for failure as it will be incredibly difficult to monitor the quality of the product.

The test documentation should also cover test procedures for the cases where subtests cannot be automated. Under this scenario, it is necessary to document how to manually test the sub-feature.

As work begins on the development of the FPGA design, there should be regular design and verification reviews as part of the engineering process to ensure that there are no changes to the plan. These reviews will provide a forum to communicate any changes that may be needed to work around implementation issues and to clear up any areas of ambiguity in the specifications. As a result of these meetings, the specifications should be updated and reviewed. If the recommended changes will impact the high level functional specification or any of the interfaces with the FPGA, there should be formal reviews with the relevant personnel to reach closure on the changes.

In summary, the main purpose of a specification is to communicate information between teams such that the design meets the requirements and can be adequately staffed to deliver on the requirements in the specified timeframe.

The requirements for the functional specification and test specification will be driven by your Company's policy on standards compliance, e.g. ISO 9001 compliance. This book does not discuss the details on ISO 9001 compliance. A detailed description of the ISO 9001 standard is available from http://www.iso.org.

Recommended further reading:

Requirements by Ian Alexander

# **Chapter 4 Resource Scoping**

#### 4.1 Introduction

This chapter is broken down into three main sections. The first section deals with engineering resources. Whether you use internal resources or whether you use external contractor resources.

The second section deals with IP. Do you have IP within the company that you can reuse, or do you use third party IP?

The third and last section deals with device selection. This details how to select the right FPGA with the right resources for your application. It covers the various techniques that you can use to help choose the right device to enable you to meet your project schedule.

#### **4.2** Engineering Resources

The assignment of engineering resource to the project is a project management task. It is key that you adequately resource the project with the appropriate personnel for the tasks in the project. When you are working on the FPGA its not only FPGA designers that you need to consider, you need to look at the team of engineers that are required to create the design. So, from a hardware engineer's perspective you look at who are the engineers that are going to work on the FPGA design. There are the RTL designers, there are the engineers with the experience integrating the design in the FPGA design software and the engineers with design verification experience.

In some companies these roles will be performed by the same individual, or the same pool of engineers. However, depending upon the size of the design or the complexity of the project you may well require a team of engineers with different skill sets from the different engineering disciplines. From a hardware engineering perspective, you also need to look at the board design, so you will to need to ensure that you have board layout engineers on the team. They will have to work close with the FPGA designers, so you want to make sure that the members of the team have a good working relationship. If you are creating a high speed design, particularly if you are

16 4 Resource Scoping

looking at design with high speed transceivers or high speed memory interfaces you are likely going to need someone on the team with signal integrity experience.

If your design uses a soft processor such as the Nios® II processor form Altera, you will also want software engineers on the team. Even if the FPGA is interfacing with a microprocessor, you still want the software engineers to be available for when you start to debug the design on the board. You also may need engineers with other system specialties on the team. For example if your design contains DSP algorithms the individual that created the algorithm may not actually be a hardware engineer, thus will not be implementing the design in the FPGA. You need to ensure that the Specialist is available for advice during the design cycle and for debug of the design after implementation. Similarly, for other IP areas of excellence; examples being the main interface protocols such as PCIe or GigE.

An important decision in the assignment of engineering resources is the decisions as to what are you going to implement with the engineering resources that exist in the company vs. what will you implement with external consultants.

#### 4.3 Third Party IP

You need to look at what third party IP is available and will be used in the design. Similarly what internal IP will be reused, do you have IP available from other projects targeting this FPGA family. Or if you are using third party IP you will probably want to look at what are you getting with the IP, do you get a consultancy service or what is your level of confidence that the IP will meet your exact requirements in terms of area, speed and functionality.

#### 4.4 Device Selection

There are seven main factors that influence your choice of device. These are:

- Specialty silicon features. Are there certain capabilities that you need that dictate

that you use a particular FPGA because they are not available in other FPGA

devices.

- Device density. How much logic will your design require? What is the mix of logic to memory blocks to dedicated multiplier blocks that is needed for your application. This will have a big impact on the price of the device that you need.

- 3. Speed requirements. This will impact the family that you choose and the speed-grade that you need to use. Once again this will have a large impact on the price of the device.

- 4. Pinout of your device. What kind of package do you require? The choice of package type and the number of I/O in your design will impact both the FPGA

4.4 Device Selection 17

cost and the board design. The package type will also influence the signal integrity and performance of the I/O in your design.

- 5. Power. What is your power budget for the design and which device is going to help you meet the budget?

- 6. Availability of IP.

- 7. The availability of silicon. You want to make sure that production silicon is available when you need it.

So these are the areas that we need to look at in more detail.

#### 4.4.1 Silicon Specialty Features

The first area that you want to look at is the dedicated resources on the device. Does your design require high speed serial interfaces and if so, how many channels and at what performance. Many of the FPGA devices that are available together come with transceivers. The performance of transceivers tends to fall into three ranges, up to 3.125 Gbps, up to 6.5 Gbps and 10 Gbps+. These are important factors in the decision process as they impact both the performance of your design and the cost of the FPGA. You also need to look at your bandwidth requirements. Both the speed of the transceivers and the number of transceivers will determine your bandwidth. Take for example the communications market; if you are trying to implement 100 Gbit Ethernet, you will likely want a minimum of ten channels of 10 Gbps transceivers.

Similarly, if you are completing a design which is math intensive such as a DSP encryption algorithm or radar application, you will require a device with a large number of DSP blocks and adequate RAM blocks to interface with the DSP blocks. The configuration of the DSP blocks is also important. The depth and number of memory blocks will impact how much processing can be performed on chip vs. having to use external memory. Internal memory is important in DSP for caching of processing results between stages of the processing algorithm. You also need to look at both the number and configuration of the dedicated DSP blocks. What is the width of the multiplication operations that you need to perform? If the DSP block does not have sufficient width, you will have to start combining DSP blocks with logic to implement your functionality. This can impact the performance of the operation that you are performing.

How many internal RAM blocks do you need? This is becoming increasingly more important as we look at designs that make use of soft processors. Being able to use internal memory blocks as cache can significantly increases the performance of the soft processor. The sizes of block RAM that is available is also important. If your design will use a lot of FIFOs, it's the number of RAM blocks that are available that matters and not the amount of bits available. FIFO's are notorious for wasting memory bits when implemented in memory blocks.

You also need to consider the debug of your design. Internal block memory is often used in the debug cycle for storing the data from embedded logic analyzers for examination.

#### 4.4.2 Density

When selecting the density of the device, it is unlikely that you will be fortunate enough to have the completed design to determine the size of device needed. You will be choosing the device based upon previous experience. Many designs are based upon previous generations of the design. This can be aid in the device selection process. You should recompile the previous design or the portions that will be used at your target FPGA family to get ballpark density estimates. If you have IP that you will be using, compile it to add to your area estimates and if you are evaluating IP for third party vendors, get an area estimate from the vendor. So, use the previous generation of the design, if it exists, add in the area requirements from IP and then using your experience, add in how much additional resources will be used for the new functionality. Once you have done this, add an additional 25% on top. You should always target a larger device than you think you will need; this is where the extra 25% comes into the equation.

You should always target a larger device than you think you will need. Designs have a nasty habit of growing and you want to guarantee that the design will fit in the targeted device and be able to close timing. You don't want to be struggling to meet timing in a 95% utilized device or be put in the position of having to pull functionality out of your system just to fit in the targeted device.

Another benefit of using a larger device is that it can help you get to in-system checkout quicker. If there is headroom in the device, the place and route software will likely not have to try as hard to meet timing and will result in shorter compile times. This benefits both the hardware and software engineer. The sooner that you have functional silicon, the sooner the software engineer can accelerate his code development process by trying it out on the targeted hardware. You can start the debug of the hardware and software much earlier in the design cycle.

Another benefit of the additional headroom in the device is that it makes it easier to accommodate late ECOs in the device or accommodate growth in future versions of the design after production.

After you have the design working functionally on the device and if there is significant unused resources on the device, you can retarget the device to a smaller device to reduce cost and not have to worry about impacting the project schedule. Some of the FPGA vendor design tools have features that enable you to migrate between device densities in the same family while maintaining the same pin-out. These features restricts you to using only the I/O resources that exist across the density ranges selected in the targeted family; the benefit being that you can retarget your design to a larger or smaller density device avoiding a board re-spin. If this feature is not available in your FPGA vendor software you can design the capability in manually by referencing data sheets and application notes. The manual process is painful and prone to user error, but is worth the investment if the automated flow is not available.

The key point is that you need to ensure that the ability to migrate between device densities while maintaining the pin-out capability is available in the FPGA family that you are considering for your application.

4.4 Device Selection 19

The recommendation is that you select a device that can migrate up in density to accommodate future design growth and can migrate down in density to allow for possible cost reduction.

This functionality is very useful if you intend to ship variations of your product at different price points with changes in the functionality. This enables the same board to be shipped. A single design can be created and functionality removed from the FPGA at the lower price points. Normally the same FPGA is shipped on the same board with a different programming file based on the reduced functionality of the design. By maintaining the same pin-out you can now remove the functionality and retarget the design to a smaller device, further cost reducing your bill of materials.

#### 4.4.3 Speed Requirements

This can be determined from your previous design experience. You should compile designs or design blocks that you already have to get an indication of the performance that they get in the targeted device. This can be used as a good best case indicator as to what you can expect from other design blocks.

The FPGA vendor's data sheets are also a good source of information on performance. They will tell you the absolute maximum that you can hope to get in terms of clock and I/O performance. While these numbers are achievable, it is likely to increase your timing closure cycle achieving these numbers, thus you should back off the numbers by approximately 15% to give you a margin of safety for timing closure.

The choice of speed-grade will impact the price of the device. When choosing device, we recommend that you always start with the fastest speed-grade to enable you to get the device on the board as soon as possible to start software debug and hardware functional check out as early as possible. If the design meets timing comfortably in the fastest speed-grade, you will benefit from faster compilations as the place and route engine does not have to try as hard to close timing. Later in the design cycle, there is the option to retarget the design to a slower device after the functionality is close to complete, for cost reduction purposes.

#### 4.4.4 Pin-Out

The type of I/O interfaces that you need for the design will impact the number of pins required and the package type. You need to understand the I/O standards that you need, the requirements for drive strength. How many pins do you need? What are the power supply requirements? A good way of determining these requirements without the design is by looking at what your device will interface with on your board. You also need to look at the signal integrity requirements for the design. Does your design have interfaces with a large number of pins that are likely to toggle simultaneously;

20 4 Resource Scoping

if so, will you have SSN issues? It is worth noting that wirebond packages typically have worst signal integrity and I/O performance than flip chip devices.

It is recommended that when looking at the pin count for your design, that you reserve pins for in-system debug. The target should be a minimum of 15% of the device pins. They can be used to route internal signals off-chip for analysis with a logic analyzer.

#### 4.4.5 Power

You know the power budget for your design based upon the specification. How many power supplies will be required for the device? Most modern FPGA devices require multiple power supplies as they have separate power planes for the core, I/O's and often the transceivers. The more power supplies that are required, the more expensive the component cost on the board and the more complex the board design.

Once again, your previous FPGA design experience will come into play. Chapter 7 in the book is dedicated to power estimation; it will help master this challenge.

To summarize, it is recommended that you use the FPGA vendor's power estimation spreadsheet together with your previous experience to determine the power that your design will consume.

#### 4.4.6 Availability of IP

IP may be available for a particular family of devices but may not have been ported to or verified on the particular FPGA family that you are considering using. This is often the case with devices that are new to the market. Interface IP in particular is a challenge for devices where the silicon has been available for less than 6 months. The devices are normally not fully characterized thus the timing models are preliminary. High performance interface IP cannot be guaranteed to close timing until the models are final.

#### 4.4.7 Availability of Silicon

If you have a project on the bleeding edge of technology, the chances are that you will be considering using the latest FPGA devices on the market. You will also likely be considering the latest FPGA device knowing that in the future, the pricing will be more favorable. The decision to use the latest FPGA devices on the market makes financial sense if the design will be going into production in 12 months but you know that your volumes will be shipping for 5+ years such that you will be hitting volume production when the FPGA process has matured and pricing is at its lowest.

4.4 Device Selection 21

#### **4.4.8** *Summary*

We really recommend that when choosing FPGA technology that you quickly stitch together dummy designs effectively to enable the process of successful device selection. You are going to have a good idea of what type of interfaces you are going to need on your device. This will help you to determine the pin requirements and simplify the I/O planning requirements. By creating the dummy design you get an idea of the utilization that you can expect to get out of the device in terms of resources. It will also provide a good guide to the performance that you can expect for your type of design. It also enables you to perform an early power estimate for your design. The creation of a dummy design is instrumental in selecting the appropriate device and should include any known IP blocks that you are going to be used in the design.

# **Chapter 5 Design Environment**

#### 5.1 Introduction

The FPGA design environment is best expressed as a combination of all of the tools, techniques and equipment that is required to successfully complete a FPGA system design. The design environment in each company is usually somewhat unique in that it has been customized to meet the needs of the company. However, there are some common elements that exist across all design elements. The goal of this chapter is to make you aware of the bare minimum requirements for a design environment that will enable the successful creation of an FPGA design on time. The design environment can be represented by five main elements.

- 1. A scripting environment

- 2. Interaction with Version Control software

- 3. Use of a problem tracking system

- 4. A regression test system

- 5. Data collection for analysis

#### 5.2 Scripting Environment

One of the challenges for engineers that are designing with FPGA devices, is when to use a scripted design flow vs. when to use the GUI in the FPGA design environment?

Scripts are ideal in the following scenarios:

- 1. Creation of projects

- 2. Creation of assignments for the design

- Compilation of designs. In particular if you utilize a compute farm environment.

A compute farm environment enables you to fire off batch jobs to the server for compilation

- 4. Functional verification and regression testing

- 5. Integration with version control software

This covers most of the FPGA design flow. It may appear that it is recommended to use scripting for every part of the design flow. This is partially true. You really should deploy scripting for any repetitive tasks. It helps other users to easily reproduce your environment and results.

So, when is it recommended to use the GUI?

The GUI should be used for the parts of the design flow that are interactive. Areas where your actions will change based upon the results that you get. Examples would be the following scenarios:

- 1. In-system debug of your design

- 2. Floorplanning operations. This could be looking at the details of the floorplan to gain a better understanding of the device architecture or the resources that are available. This could also be creating a physical layout of your design in the floorplan in a team based design environment

- 3. Getting started with new tools. The GUI provides a great way for setting up your first project and uncovering the features and capabilities of the tool. Once familiar with the tool, it is recommended that you move to a scripting environment

Through the use of scripting you can save time and effort on repetitive tasks. One of the big benefits is that it simplifies the passing of tasks between team members in a team based design. If someone is taking over a project or design block, from another engineer; Rather than having to write detailed instructions describing what needs to be done to get your results, you give them the script which is self documenting. The new engineer reads the script, runs the script and they get started from where you left off on the project. Nearly all EDA tools that are part of the FPGA design flow have scripting interfaces, both a command-line interface for creating batch files and assignment scripting for creating settings in the project. Most of the EDA industry has standardized on Tcl as the scripting interface for tool assignments.

#### 5.3 Interaction with Version Control Software

Revision Control software provides a record of the history of changes to your design. When you are designing a FPGA, it is necessary to understand the minimum set of files that is needed for check-in and check-out of the version control system. You need to minimize the number of files because the more files that you check-in, the more storage you will need and the more complex the operation will become. Each time you make a change to your design you need to check the FPGA project back in to the version control software. A good scripting environment helps to simplify this process. The initial set-up of the scripts and the identification of the files that need to be checked in and out may be complex. However, once the scripts are established, the scripts can be shared among the engineers that are working on the project. If you can recreate or describe your project with a script, the version control interaction becomes much simpler.

Different FPGA design tools require different sets of files to be placed under version control in order to recreate the results; so the set-up that you use for one FPGA vendor may differ significantly than the set-up used for another. The principle however is the same. If the tools use text files, the interaction with version control systems is much simpler than tools that use binary files that store critical information.

To date, FPGA vendors have done a poor job in publicly documenting which files need to be checked into version control software to enable you to recreate the results of the previous compilation. This process becomes more complex if you use multiple tools in the FPGA design flow. It is recommended that you contact the vendors of each of the tools to understand their recommendations.

One of the major influences on how you use a version control system is the directory structure that you are using for your design environment. This comprises of the location of the RTL design files, location of the RTL and IP libraries, "c" code and programming image if you are using a soft processor, simulation testbenches, location where the results of your regtests are stored and the scripts to compile the design in the FPGA software or in other EDA software. You need to be able to link all of these elements together successfully using the correct versions of the files.

You want to avoid the situation were you are trying to debug the design in the lab and you are using the wrong programming image for the FPGA, or you are loading the soft processor with old source code, or a designer is making changes to an out of date version of the RTL. Proper use of version control will provide an environment that prevents these scenarios from occurring. You also want to be able to store the report files in version control as the report files document the status of the design. This provides valuable information to other designers that work on the same project.

## 5.4 Use of a Problem Tracking System

A problem tracking system is not a capability that you get from your FPGA vendor. However, I can guarantee that it is a tool that FPGA vendors use as part of their engineering and product planning process. Problem tracking systems tend to be homegrown systems to meet the needs of the individual company. In fact many of the EDA tool and FPGA vendors have a customer interface to their systems for submitting problem reports.

There are commercial systems available on the market. These systems are essentially database system with a customizable front-end to meet your companies needs. In your design environment, you will use the system to track all known issues with your FPGA design. It enables the design engineers to document problems with the design as they occur. This provides the team with an instant status on the design and can be used to track the stability of the design throughout the design process. It makes the other members of the team aware of the problems with your design, avoiding the case were they are trying to debug a problem in their part of the system that is being caused by your design. By looking at this data it can be determined

whether to use a particular project build or whether to revert to an earlier build that did not exhibit the problems that were introduced into that particular build.

It also enables users to document the closing of issues. This enables the team to collaborate on solving the issues in the design. This is very helpful in a team based design environment that spans multiple time zones.

As mentioned, the system can be used to provide a snapshot of the health of the project. To do this, it needs to be linked to the regression test system such that test failures automatically file problems reports in the tracking system against the build that is being tested.

## 5.5 A Regression Test System

As part of your testing, the design engineers will create point tests to show that the design meets functionality. It must be a requirement that you have a set of tests that are run regularly on the design to provide a health check on the design. These tests give you confidence that as your design changes that you do not reintroduce old problems or break existing functionality. Regression tests are discussed in more detail in Chapter 11.

## 5.6 When to Upgrade the Versions of the FPGA Design Tools

One of the challenges that you will face if you have a design that spans more than 6 months is when to adopt new releases of the tools that are used in the FPGA design environment. FPGA vendors typically have at least two major releases per year plus a selection of service pack releases that include bug fixes and timing model changes. When should you freeze the version of the design tools that you are using?

This decision will be driven by where you are in the design flow. If you are in the early stages of the design, then you should update to the latest release of the FPGA design software unless you are aware of serious problems with the software. This will give you access to the latest bug fixes and features in the software. Normally there is some degree of compile time improvement in the major releases of the FPGA design software.

If your design is mostly complete and the version of the FPGA vendor software that you are using contains the final timing models for the devices that you are targeting, then you should consider freezing the version of the design software that you are using. An exception would be if you come across a bug in the design software that impacts your design. This will likely require you to upgrade the design tools to access the fix to the bug.

If your design is close to complete but the FPGA vendor timing models are still preliminary you will have to upgrade the version of the design software once the

final timing models become available. This can be problematic as it may require you to upgrade the versions of the vendor IP blocks, possibly creating more work for you; in particular in verifying the design. It is strongly recommended that you verify your design against the production or final version of the FPGA timing models.

Some of the FPGA vendors provide the capability to read a database from one version of the design software in a later release of the software. Thus the design does not have to be recompiled and only timing analysis rerun to verify that the design still meets timing, with the final timing models.

## 5.7 Common Tools in the FPGA Design Environment

FPGA design software: This comes from the FPGA vendor and includes the FPGA Place and Route Software and Timing Analysis tools. The major FPGA vendors also include RTL Synthesis, Advanced Timing Closure Features. On-Chip debug and Floorplan Tools.

FPGA synthesis software: This may come from the FPGA vendor or may come from EDA synthesis tool vendors such as Synopsys or Mentor Graphics. Most FPGA synthesis tools support Verilog and VHDL. Some of the tools now support SystemVerilog.