# Module 4 B2 Electronic Fundamentals

# AERO-Bildung Aviation Training Center

| 1 SEM                         | I-CONDUCTORS                     | 5  |

|-------------------------------|----------------------------------|----|

| 1.1.1 Int                     | troduction to Semi-conductors    | 5  |

| 1.1.2 Se                      | emi-conductor Doping             | 9  |

| 1.1.3 Se                      | emi-conductor Materials Tutorial | 12 |

| 1.2 DIODE                     | ΞS                               | 13 |

| 1.2.1 Th                      | e P-N Junction                   | 13 |

| 1.2.2 Re                      | ectivier/ Normal Diode           | 16 |

| 1.2.3 Ha                      | alf Wave Rectification           | 19 |

| 1.2.4 Fu                      | III Wave Rectification           | 20 |

| 1.2.5 Di                      | ode Testing                      | 22 |

| 1.2.6 Lię                     | ght Emitting Diodes (LEDs)       | 27 |

| 1.2.7 Ze                      | ener Diode                       | 28 |

| 1.2.8 Th                      | ne Shottky Diode                 | 32 |

| 1.2.9 Va                      | aractor Diode                    | 33 |

| 1.2.10                        | Photo-Diodes                     | 34 |

| 1.2.11                        | Voltage-Sensitive Components     |    |

| 1.2.12                        | Photo -Conductive Cells          |    |

| 1.2.13                        | Thyristor                        | 38 |

| 1.2.14                        | The Triac                        |    |

| 1.2.15                        | The Diac                         |    |

| 1.2.16                        | Tutorial Sheet 2.2: Other Diodes |    |

| Tutorial Sheet 2.1 Solutions  |                                  | 42 |

| Tutorial Sheet 2.2: Solutions |                                  |    |

| 1.3 TRAN                      | SISTORS                          | 46 |

| 1.3.1 The NPN Transistor                    | 46  |

|---------------------------------------------|-----|

| 1.3.2 The PNP Transistor                    |     |

| 1.3.3 Gain                                  | 50  |

| 1.3.4 THE TRANSISTOR AS A VOLTAGE AMPLIFIER | 52  |

| 1.3.5 The Transistor as a Switch            | 65  |

| 1.3.6 Coupled Amplifiers                    | 68  |

| 1.3.7 Common-Emitter Amplifiers             | 68  |

| 1.3.8 The Common-Collector Amplfier         | 73  |

| 1.3.9 The Darlington Pair                   | 75  |

| 1.3.10 The Common-Base Amplfier             | 76  |

| 1.3.11 Coupled Amplifier Comparison         | 78  |

| 1.3.12 Amplifier Classes                    | 80  |

| 1.3.13 Oscillators                          | 96  |

| 1.3.14 Multivibrators                       | 103 |

| 1.3.15 Field Effect Transistor              | 119 |

| 1.3.16 MOSFETS                              | 128 |

| 1.4 INTEGRATED CIRCUITS                     | 135 |

| 1.4.1 Operational Amplifiers                | 135 |

| 1.4.2 Op-Amp Parameters                     | 151 |

| 1.4.3 Non-Inverting Amplfier                | 163 |

| 1.4.4 Voltage Follower                      | 166 |

| 1.4.5 Inverting Amplifier                   | 167 |

| 1.4.6 Op-Amp Troubleshooting                | 174 |

| 1.4.7 Comparators                           | 178 |

| 1.4.8 Summing Amplifier                     | 182 |

|                                             |     |

Issue: 20/11/2013

- For Training Purpose Only -

5

| 1.4.9 T | he Integrator                   |     |

|---------|---------------------------------|-----|

| 1.4.10  | The Differentiator              |     |

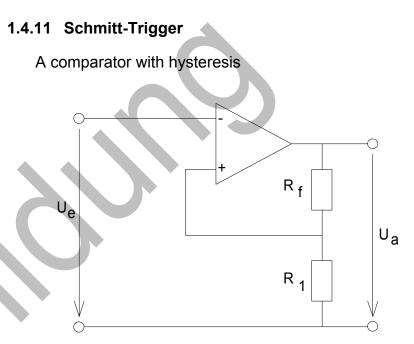

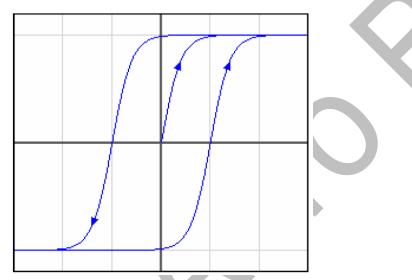

| 1.4.11  | Schmitt-Trigger                 | 197 |

| 1.4.12  | Integrated Circuit Technologies |     |

####

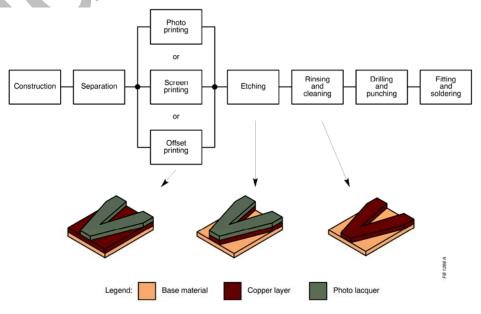

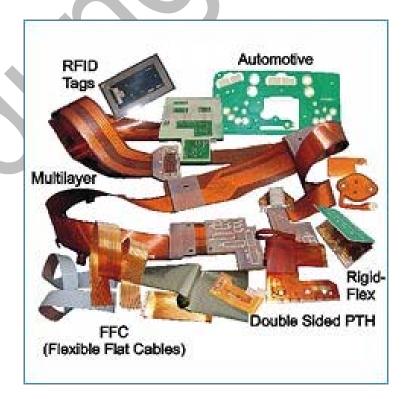

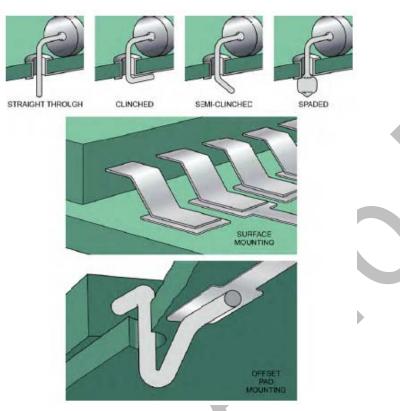

| 2.1 TYPES OF CIRCUIT BOARDS    | 201 |

|--------------------------------|-----|

| 2.2 CONVETIONAL CIRCUIT BOARDS | 201 |

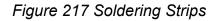

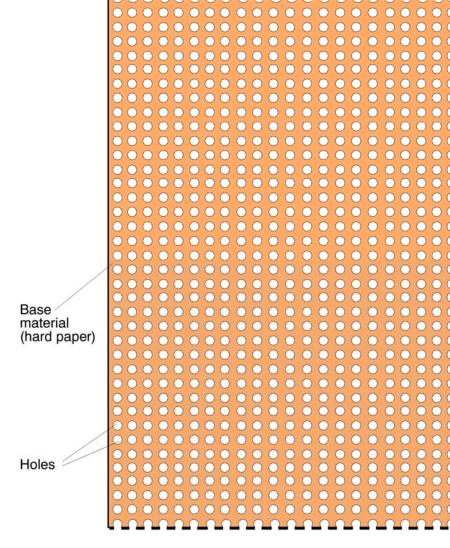

| 2.2.1 Soldering Strips         | 201 |

| 2.2.2 Raster Boards            | 202 |

| 2.2.3 Tag Raster Boards        | 203 |

| 2.2.4 Veroboards               |     |

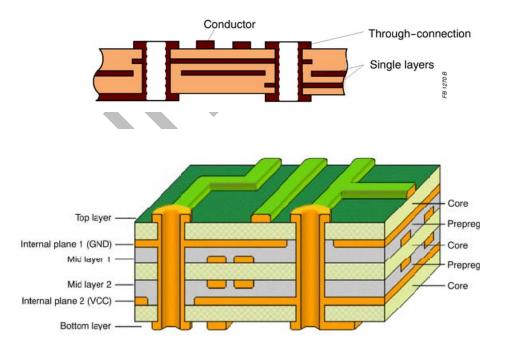

| 2.3 PRINTED CIRCUIT BOARDS     | 205 |

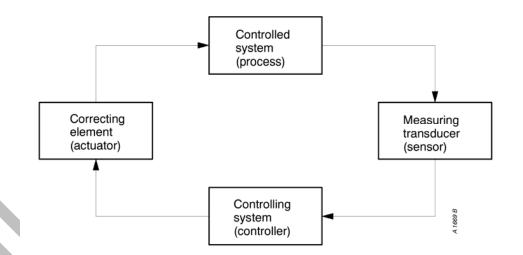

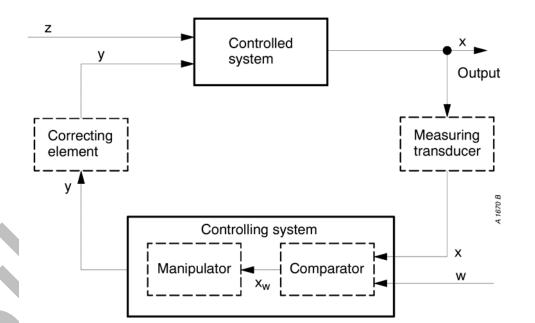

# 3 SERVOMECHANISMS......220

| 3.1 INTRODUCTION                          | 220 |

|-------------------------------------------|-----|

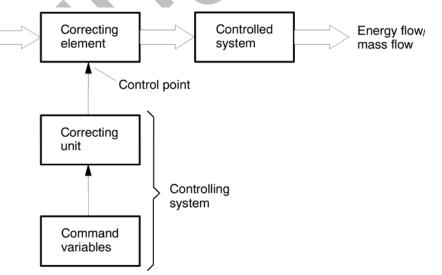

| 3.1.1 Control Systems                     |     |

| 3.2 TYPES OF SERVOMECHANISM               | 223 |

| 3.2.1 Open Loop Systems                   | 223 |

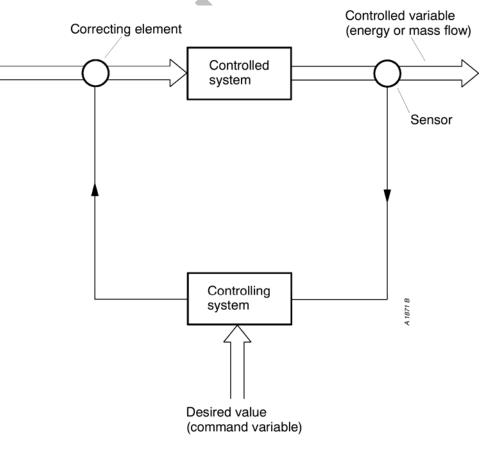

| 3.2.2 Closed Loop Control System          | 224 |

| 3.2.3 Control Response                    | 229 |

| 3.3 AC SERVO MOTORS                       | 233 |

| 3.3.2 Rate Servos                         | 237 |

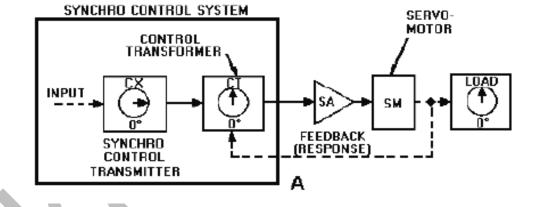

| 3.4 REMOTE INDICATING SYNCHRONOUS SYSTEMS | 239 |

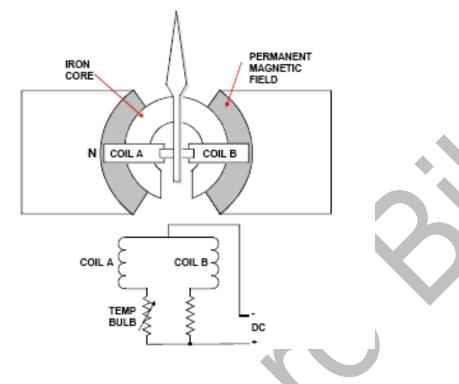

| 3.5 DC S | YNCRO SYSTEMS                                   | 239    |

|----------|-------------------------------------------------|--------|

| 3.5.1 D  | esynn Systems                                   | 241    |

| 3.6 ALTE | RNATING - CURRENT "SYNCHRONOUS" SYST            | EMS246 |

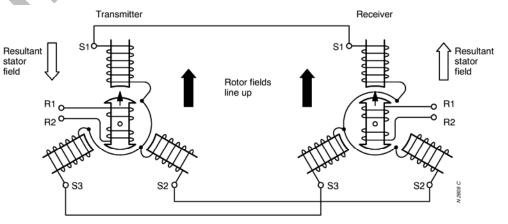

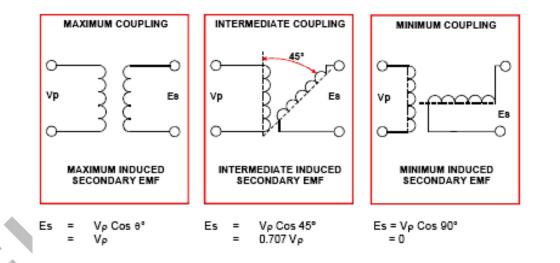

| 3.6.1 P  | rinciple of Operation                           | 247    |

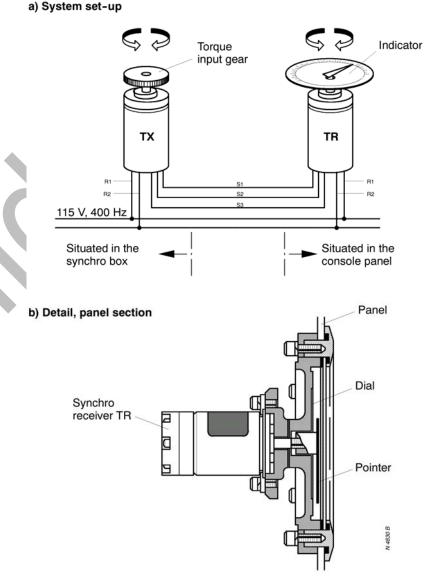

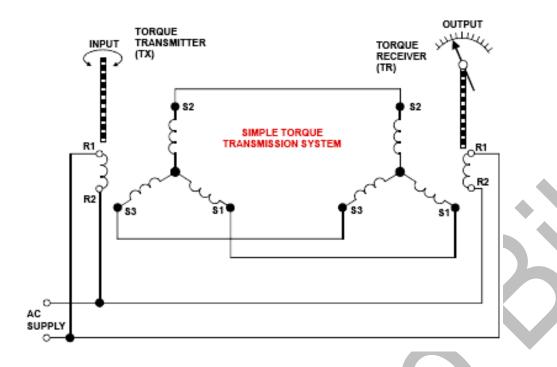

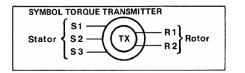

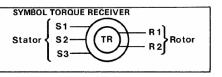

|          | orque Synchros                                  |        |

|          | TROL SYNCHROS                                   |        |

| 3.8 RESC | DLVER SYNCHRO                                   | 256    |

| 3.9 STAN | IDARDISATION OF SYNCHROS                        | 258    |

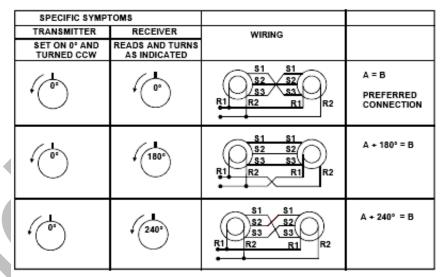

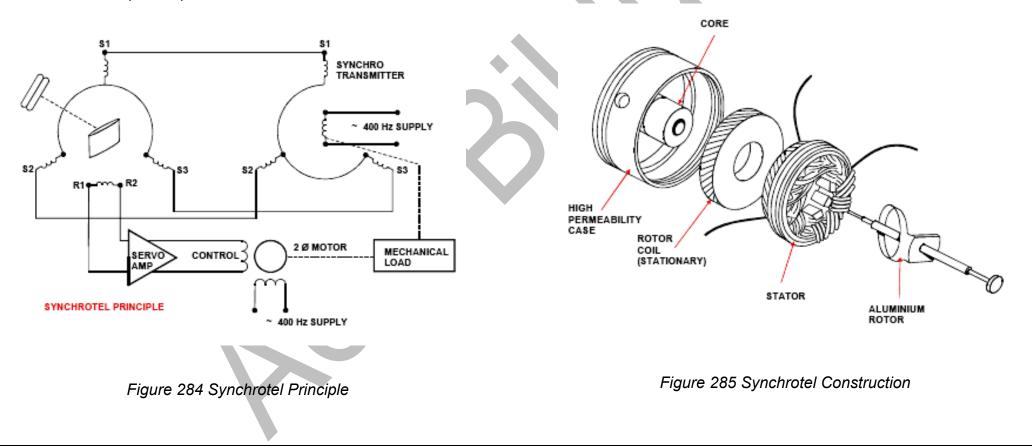

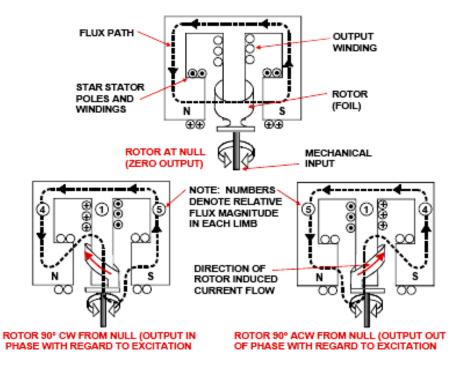

| 3.10SYNC | CHROTELS                                        | 259    |

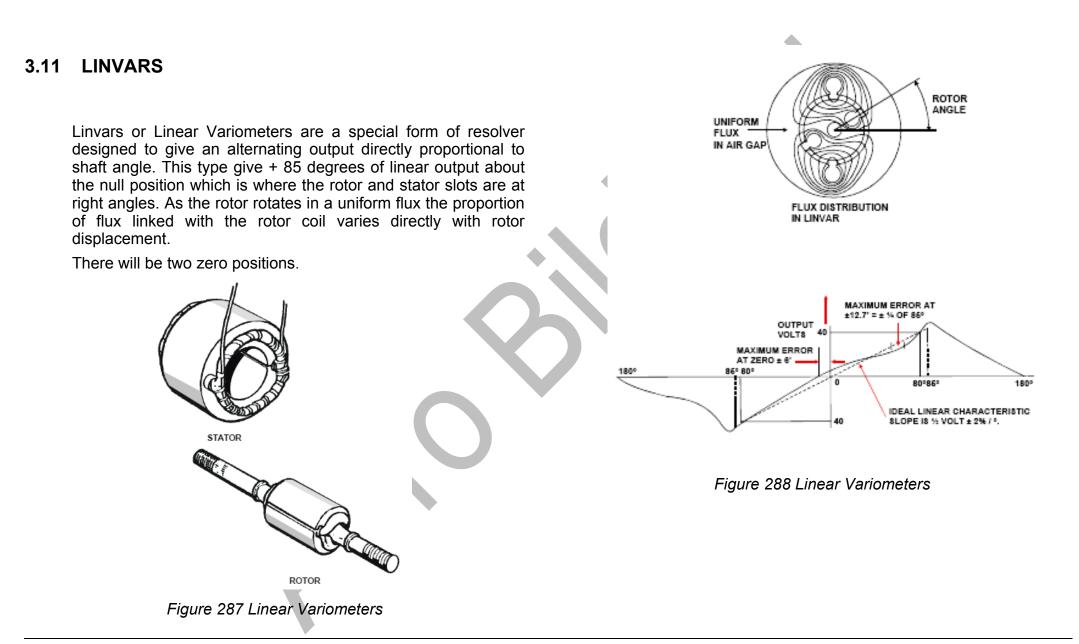

| 3.11LINV | ARS                                             | 261    |

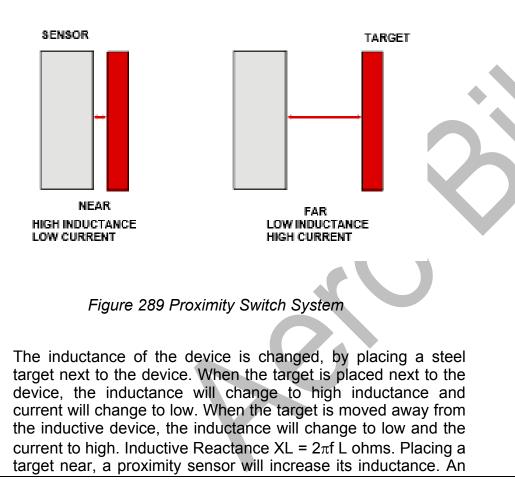

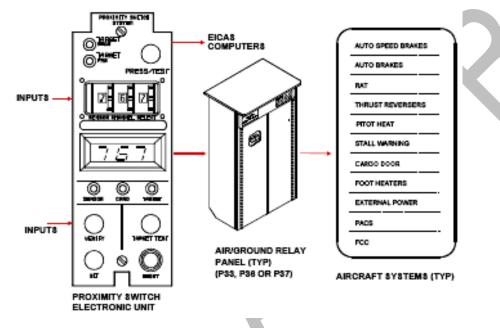

| 3.12PROX | KIMITY SWITCH SYSTEM                            | 262    |

| 3.12.1   | Application                                     |        |

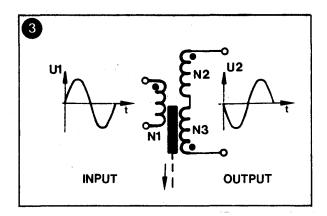

|          | AR VARIABLE DIFFERENTIAL TRANSFORMER            |        |

| (LVD     | Г)                                              | 265    |

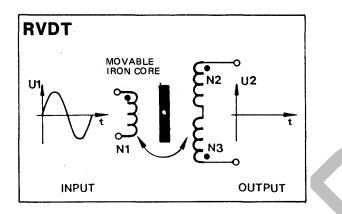

| 3.13.1   | Rotary Variable Differential Transformer (RVDT) | 267    |

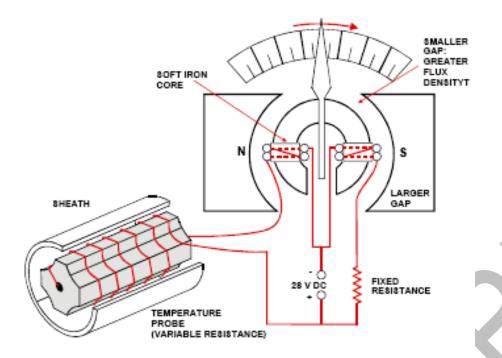

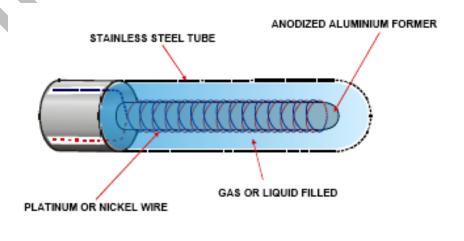

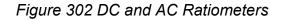

| 3.14DC A | ND AC RATIOMETERS                               | 267    |

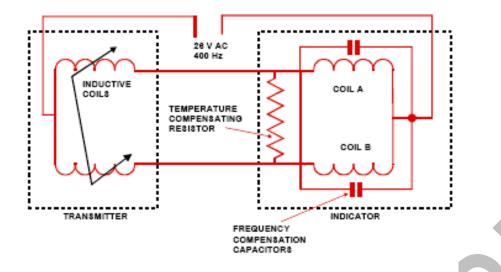

| 3.14.2   | AC Ratiometer                                   | 270    |

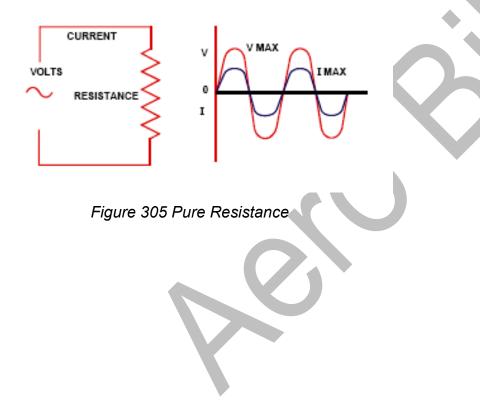

| 3.14.3   | Pure Resistance                                 | 273    |

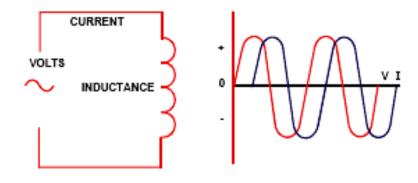

| 3.14.4   | Pure Inductance                                 | 273    |

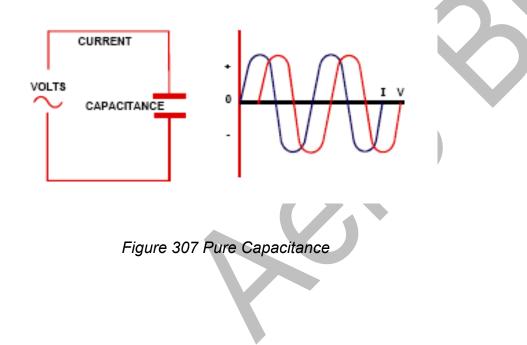

| 3.14.5   | Pure Capacitance                                | 274    |

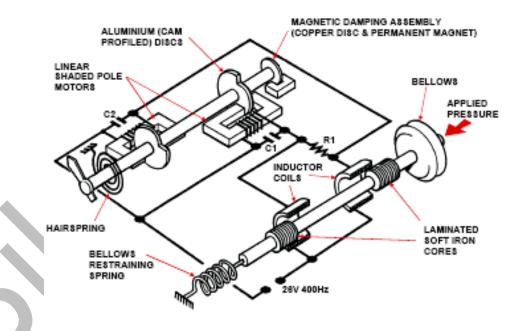

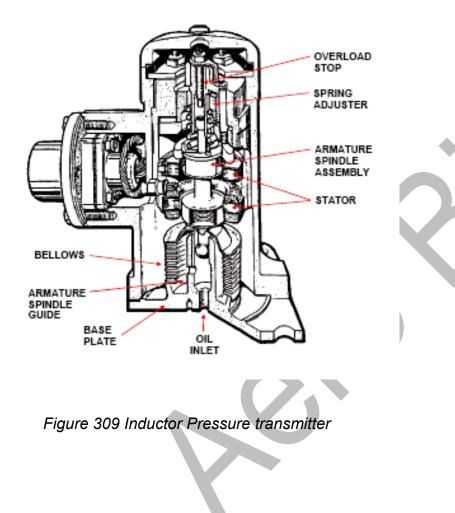

| 3.14.6   | Inductor Pressure Gauge Circuit                 | 274    |

| 3.14.7   | Inductor Pressure Transmitter                   | 275    |

|          |                                                 |        |

# 4 LIST OF FIGURES......278

# **1 SEMI-CONDUCTORS**

### 1.1.1 Introduction to Semi-conductors

A semi-conductor is a class of crystalline solids. Its energy state is indeterminate between that of an insulator and a conductor. A pure semi-conductor is known as an 'Intrinsic semiconductor'. For example, 99.99% pure silicon is known as "High purity" silicon.

An intrinsic semi-conductor is a poor conductor (good insulator) and is very dependant on temperature. The resistance of a semi-conductor decreases with an increase in temperature. This is known as a "negative temperature co-efficient".

Examples of intrinsic semi-conductors are Silicon, Germanium and Gallium Arsenide.

The main semi-conductor in commercial use is Silicon. Silicon is a base material in sand; hence it is in abundant supply.

# **Electrons and Current Flow**

An electron is a physical particle with a negative charge.

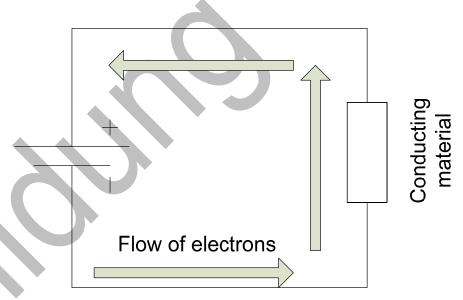

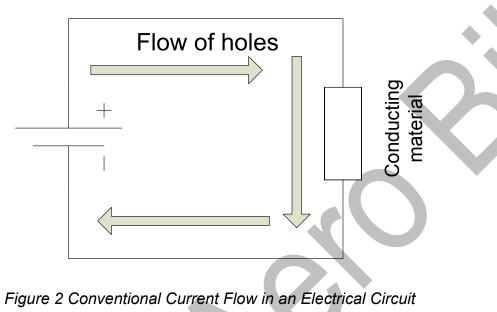

When a battery is placed across a conductor the electrons will be attracted to the positive terminal of that battery. Figure 1 illustrates the actual current flow when a power supply is connected across a conducting circuit. Electron current flow is 'Negative-to Positive'.

Figure 1 Actual Current Flow in an Electrical Circuit

A hole is not a physical particle. It is simply the space (missing bond) remaining after an electron vacates the outer ring of an atom during current flow.

However, a hole can be treated as a physical particle because it has a positive charge and moves in exactly the opposite direction to the flow of electrons. When a battery is placed across a conductor the holes will be attracted to the negative terminal of that battery. This is known as conventional current flow. Figure 2 illustrates the conventional current flow when a power supply is connected across a conducting circuit.

Conventional current flow is 'Positive to Negative'

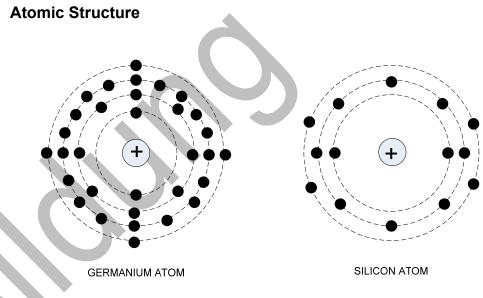

Figure 3 Atomic Structure of Germanium and Silicon

The atomic structures of the two most commonly used semiconductors are illustrated in figure 3. It should be noted that orbiting electrons are not arranged in an orderly manner. The above is a 2-dimensional representation of particles moving on a 3-dimensional plane. The electrons do not rotate in perfect circles or on a flat plane.

The above atoms are known as "Group 4" materials. This is because they have four electrons on their outer shell. These are known as "Valence Electrons".

### Valence Electrons

These electrons are farthest from the nucleus of the atom. They are less tightly bound by the attractive force of the nucleus. These outermost electrons have higher energy than those within the atom; this makes it easier for them to move between atoms.

The movement of valence electrons between atoms is the main factor in electrical conduction.

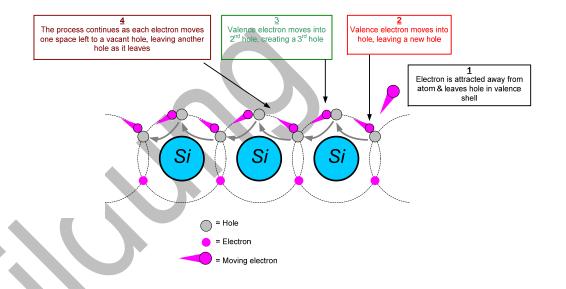

The movement of valence electrons between atoms is shown in figure 4. It should be noted that as an electron is attracted away from the atom, it leaves a hole. That hole subsequently attracts another electron, leaving another hole. For illustrative purposes, the diagram shows the valence electrons moving left to right. It can be seen that holes move from right to left (as indicated by the arrows).

## Figure 4 Movement of Valence Electrons between Atoms

### **Covalent Bonds**

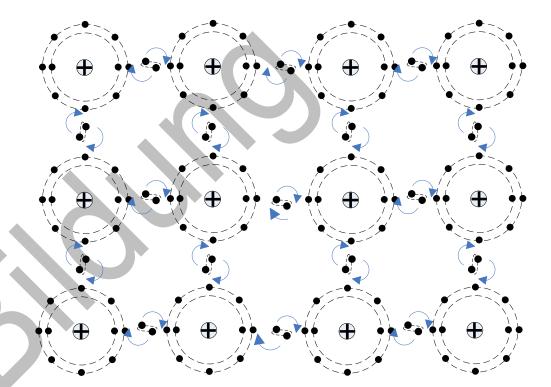

The valence electrons of a semi-conductor atom can link together with the valence electrons of other adjacent atoms. These links are known as "Covalent bonds".

As a result of covalent bonding, each atom has a half share in eight valence electrons. This linking arrangement of multiple atoms forms a stable crystal lattice.

The two-dimensional arrangements of covalent bonds in a silicon crystal lattice are shown in figure 5.

Figure 5 Co-valent Bonding of a Silicon Crystal Lattice

#### 1.1.2 Semi-conductor Doping

Semi-conductor doping is a chemical treatment performed on an intrinsic semi-conductor to either increase or decrease conductivity.

Doping improves the ability to transmit and control electrical current through the semi-conductor.

Processes also exist to further purify an intrinsic semiconductor prior to doping. This is often necessary in order to effectively control/measure the doping process.

Doped semi-conductors are often referred to as "Extrinsic Semi-conductors".

Doping involves adding a small volume of impurity atoms (usually only about 1\*10<sup>6</sup>) to the semi-conductor material.

As noted earlier, the intrinsic semi-conductor has 4 valence electrons. The impurity element is selected to have atoms with an extra electron or a missing electron (in relation to the semiconductor atom).

The addition of an impurity atom is added with the intention of altering the number of electrons in a semi-conductor.

There are two types of extrinsic semi-conductor:

- N-Type Semi-conductor.

- P-Type Semi-conductor.

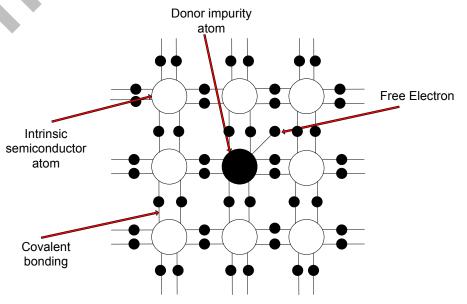

## The N-Type Semi-conductor

Group 5 materials are used to provide an extra electron after doping with the intrinsic semi-conductor. These elements have 5 valence electrons. This means that one electron is free after the covalent bonding occurs. This electron is referred to as a "Donor Electron".

These donated electrons have the effect of lowering the semiconductor's resistance, therefore making it more conductive. These electrons are un-bonded and free to wander the crystal lattice. The donor electrons will migrate through the atomic structure and can therefore act as current carriers when a low voltage is applied. Figure 6 shows the atomic arrangement after doping with the group 5 material.

Figure 6 Atomic Arrangement after Doping with Group 5 Material

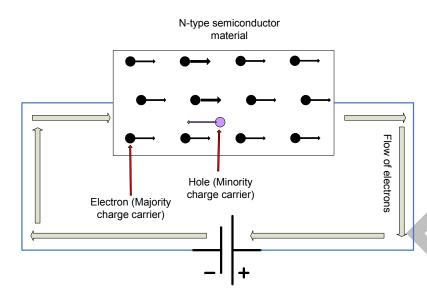

The number of free electrons can be strictly controlled by the doping process. Figure 7 shows the current flow in an N-type semi-conductor

Figure 7Current Flow in an N-Type Semi-conductor

The electron is the majority carrier in an N-type semi-conductor. The term 'N-Type' is used because the electron is negatively charged.

Due to intrinsic leakage conduction, the hole (positively charged) acts as a minority carrier in the opposite direction. It should be noted that this current is negligible in comparison to the main current flow.

Phosphorus and Arsenic are good examples of group 5 materials used in this doping process.

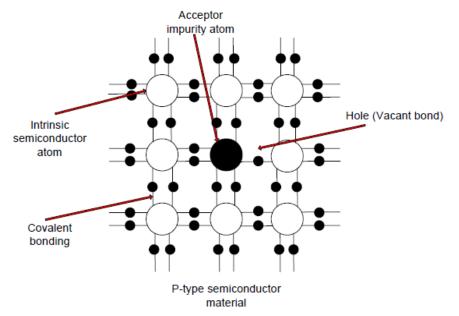

# The P-Type Semi-conductor

Group 3 materials are used to provide an extra hole after doping with the intrinsic semi-conductor. These elements have 3 valence electrons. This creates an extra hole for a valence electron already within the intrinsic material. This hole is commonly referred to as an "Acceptor".

When a power supply is applied, electrons will be attracted to the positively charged holes. The flow of electrons to these holes creates more holes elsewhere in the material. The result is a flow of charge from the positive terminal to the negative terminal. Figure 8 shows the atomic arrangement of the semiconductor after it has been doped with the group 3 materials.

Figure 8 Atomic Arrangement after Doping with a Group 3 Material

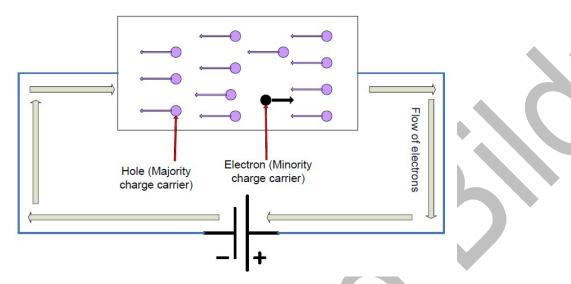

The hole is the majority carrier in this doped semi-conductor. The term "P-type" is used because the material is positively charged.

Figure 9 shows the direction of current flow in the P-type semiconductor.

*Figure 9 Current Flow in a P-Type Semi-conductor*

Due to intrinsic leakage, the electron (negatively charged) acts as a minority carrier in the opposite direction.

Indium, Aluminium and Boron are good examples of group 3 materials used in this doping process.

#### 1.1.3 Semi-conductor Materials Tutorial

All answers can be taken directly from the course text.

- 1. State the meaning of:

- a) Semi-conductor.

- b) An intrinsic semi-conductor.

- c) Negative temperature co-efficient.

- 2. Give 2 examples of an intrinsic semi-conductor.

- 3. State the semi-conductor that is used in most electronic production and give the main reason for its use.

## 4.

- a) State the properties of an electron and state the direction of actual current flow.

- b) State the properties of a "Hole" and the direction of conventional current flow

- c) Which type of current flow is most generally used when understanding and processing electrical circuits?

- 5. State the meaning of a group 4 material.

- 6. State the meaning of a Valence electron. How are they different from other electrons within the semi-conductor atom?

- 7. What is meant by 'Co-valent' bonding"?

- 8.

- a) What is meant by "Semi-conductor doping"?

- b) Why is an intrinsic semi-conductor purified further prior to the doping process?

- c) What does the doping process involve?

- d) What is an Extrinsic Semi-conductor?

- e) Describe how the impurity atoms are selected for semi-conductor doping.

- f) What are the two types of extrinsic semi-conductor?

- a) Describe the properties of a semi-conductor doped with a Group 5 material.

- b) Using a diagram, illustrate the flow of current in a semi-conductor doped with a group 5 material.

- c) State the Majority and Minority carriers.

- d) Give 2 examples of group 5 materials used in this doping process.

- 10.

- a) Describe the properties of a semi-conductor doped with a Group 3 material

- b) Using a diagram, illustrate the flow of current in a semi-conductor doped with a Group 3 material.

- c) State the Majority and Minority carriers.

- d) Give 2 examples of Group 3 materials used in this process.

# 1.2 DIODES

#### 1.2.1 The P-N Junction

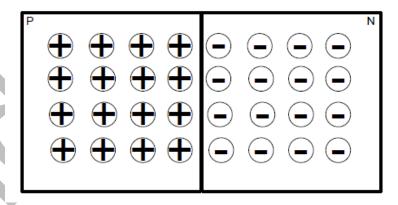

A typical junction diode structure is formed using P-type and Ntype materials. The P and N-type materials are in contact to form a P-N junction. Under the correct conditions, the holes and electrons are allowed to join (electron-hole combinations), allowing a current to flow across the junction.

As covered in the previous section, the P-type material consists of Holes as the Majority carrier. This means the P-type material is positively charged and will attract any free electrons.

The N-type material consists of electrons as the majority carrier. This means the N-type material is negatively charged and electrons will be attracted to any holes.

#### The P-N Junction without Applied Power

Under static conditions (without applied power), the P-type material has an excess of holes and a shortage of electrons (all the free electrons have filled some vacant holes, which the material still has in abundance). Inversely, the N-type material has an abundance of electrons and a shortage of holes (all the holes have been filled, leaving a significant number of free electrons). Figure 10 shows the P-N junction in the static state.

Figure 10 P-N Junction in a Static State

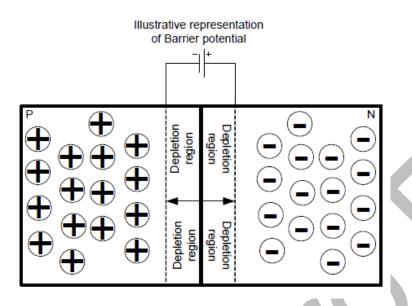

When the N-type material loses an electron (creates a hole), the charge becomes positive. When this occurs for many electrons, the area of the N-type material begins to reject holes (attract electrons).

When the P-type material holes become occupied with an electron, the charge becomes negative. When this occurs for many holes, the area of P-type material begins to reject electrons (attract holes).

This creates a depletion region of current carriers due to the lack of electron-hole combinations. In-turn a further lack of electron-hole combinations occurs. This arrangement of the P-N junction is shown in figure 11.

Figure 11 Depletion Region in a P-N Junction

The depletion region is also known as a barrier. Characteristically, the majority current carriers are repelled from the junction contact causing low current across the junction. The flow of low current is caused by the minority carriers in each material.

# The P-N Junction with Forward Bias

An electro-magnetic force (EMF) can be applied to the junction. This generally occurs in the form of an applied voltage signal, with the positive polarity connected to the P-type material.

Figure 12 Effects of a Voltage applied to the P-Type Region of a P-N Junction

Figure 12 shows the effects of a voltage applied to the P-type material. If the applied EMF is great enough to overcome the barrier, electrons (from the N-type material) and holes (from the P-type material) are attracted to the barrier. These majority current carriers combine and cause a flow of (conventional) current into the N-type region. The EMF injects fresh carriers into the junction. The current is sustained by majority carriers already in the junction. This means the current flow is large.

This state of current flow (applied to the P-type region) is known to be forward bias because the conventional current flow is positive (P-type, majority carriers are holes) to negative (Ntype, majority carriers are electrons).

The barrier potential for germanium is 0.2V - 0.3V. The barrier potential for silicon is 0.6V - 0.7V.

## The P-N Junction with Reverse Bias

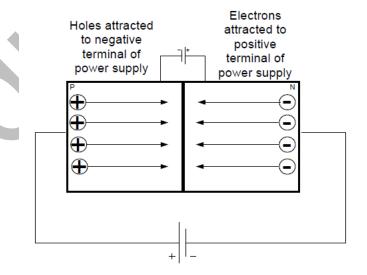

If the external EMF is reversed in polarity (the positive terminal connected to the N-type region, the negative terminal connected to the P-type region) there will be no current flow (except that due to intrinsic conduction of minority carriers).

Figure 13 Effects of a Voltage applied to the N-Type Region of a P-N

Junction

Figure 13 shows the effect of reverse bias on a P-N diode. The holes in the P-type region will be attracted to the electrons in the negative terminal of the power supply. The electrons in the N-type region will be attracted to the positive terminal of the power supply. There can be no electron-hole combinations at the junction causing the depletion region to increase (widen).

The application of an excessive reverse bias potential to a P-N junction will cause catastrophic destruction to the diode.

#### 1.2.2 Rectivier/ Normal Diode

#### The Forward Bias Diode

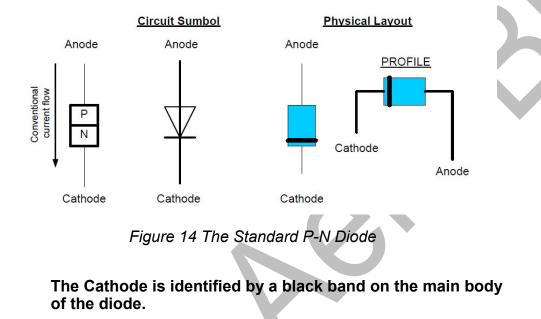

The circuit diagram of a standard forward bias diode is shown in figure 14.

It is important to note that the input to the P-type region on a diode is called the "Anode". The output of the diode from the N-type region is known as the "Cathode". The physical layout of a diode is also shown on figure 14.

#### Diode Uses

The most important point to note about a diode is that under the correct conditions it allows current to flow in one direction only (Anode to cathode or P to N).

The main use of the standard P-N diode is to convert alternating current (AC) to direct current (DC). This action is known as rectification and is discussed later.

Another use of the standard P-N diode is to block current flow in the reverse direction (Cathode-Anode). This is mainly used on digital systems to prevent current flow into an integrated circuit.

#### **Diode Characteristics**

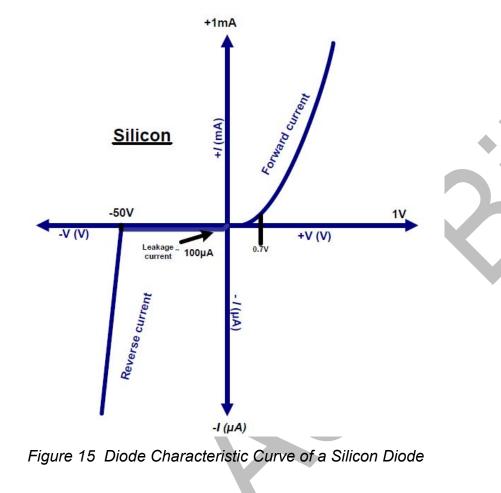

The diode characteristic curve for silicon is shown in figure 15.

The diode forward bias switch-on voltages are stated below:

- Silicon = 0.7V

- Germanium = 0.3V

When operating in forward bias, the voltage must overcome the barrier before the current can increase. Once the barrier is overcome the current flow increases exponentially with an increase in voltage. From the graphs, it can be noted that the measurements are in milliamps.

During reverse bias operation, the electrons and holes move away from the junction as the depletion region increases. A negligible current is permitted to flow due to leakage from minority carriers (usually no more than  $100\mu$ A).

### Avalanche Breakdown

As the reverse voltage slowly increases, the negative current flow remains relatively stable. Once the reverse voltage limit is exceeded, the leakage current rises to a magnitude that can be limited only by resistance.

The maximum inverse voltage (given on the specifications of practical diodes) dictates the maximum reverse voltage that can be applied to the diode before avalanche breakdown will occur.

Avalanche breakdown occurs when an excessive external reverse bias voltage is applied to the diode.

Assume that a single conduction electron gains sufficient energy from the applied power source to accelerate it towards the positively charged end of the P-N junction. As it is propelled across the junction it collides with an atom. This releases enough energy to dislodge another valence electron for conduction.

There are now two free high-energy electrons. Assume each of these electrons collides with another atom. This has now freed another two valence electrons from their bonds. This continues with each collision, effectively doubling the number of electrons each time.

This results in a rapid increase of reverse current as the number of free electrons continues to multiply. This is known as the **avalanche effect**.

# Other Characteristics of a Standard Diode

There are two other main factors that affect the operating conditions of a diode:

- Maximum forward current.

- Maximum operating temperature.

The maximum forward current should be limited (using an appropriate resistor) to prevent the junction from heating up during normal operation. When a voltage is applied to the diode and a current is allowed to flow, power is dissipated across the circuit. This power dissipation will cause the diode to heat up and produce an increase in leakage current as the junction atoms collide.

The maximum operating temperature must be observed for the same reason.

## **Diodes in Series**

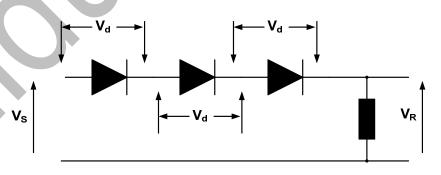

When diodes are connected in series the current is the same through each diode. It should be noted that there will be a drop across each diode equal to the bias voltage (0.7V Silicon). The maximum forward current of the diode should not be exceeded.

An example of a set of diodes in series is shown in figure 16.

$$V_R = V_S - 3V_d$$

Figure 16 Diodes in Series

Kirchoff's voltage law applies where the total drop across the diodes subtracts from the supply to leave the remaining voltage to power the load.

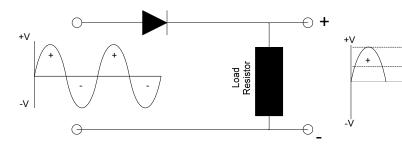

### 1.2.3 Half Wave Rectification

A Half-wave rectifier is a circuit that converts an alternating sine wave into a pulsating DC signal that consists of one-half of a sine wave for each input cycle.

The circuit in figure 17 shows the circuit of a half-wave rectifier.

Figure 17 Half Wave Rectification

An AC supply can be connected to the diode. When the supply is positive (with respect to the "P" region), the circuit is forward biased. This is referred to as the positive half-cycle. When the supply goes negative for the remainder of the cycle (the negative half-cycle), the current is blocked due the reverse bias on the junction. Therefore, the junction will only pass current on the positive half of the input cycle.

The formula to calculate the average Voltage of a half-wave rectified load is shown in equation 1a.

Equation 1a: Average Voltage of a Half-Wave Rectified Load

The improved (and quicker) method of obtaining the average voltage is shown in equation 1b.

$$V_{AV} = 0.318 \times V_{\text{max}}$$

The output from the half-wave rectifier will produce a half-sine for every cycle at the input. The output is always positive (though still variable) and is now DC.

The frequency is still equal to that of the supply frequency because the time period of the half-cycles remains the same as the time period of the input sinusoidal signal.

The diode barrier potential also has an effect on the output of the half-wave rectifier. The description above demonstrates an ideal diode; therefore it did not discuss the effects of the barrier voltage.

Equation 1b: Quick Calculation

When the diode is operating under forward bias, the input signal must overcome the diode barrier voltage (0.7V for Silicon) before it will conduct. Therefore the output voltage will always be 0.7V less than the input voltage. This is expressed in equation 1c.

$$V_{OUT} = V_{IN} - 0.7$$

Equation 1c: Effect of Diode Barrier Potential on the Half-Wave Rectifier

The Peak-inverse voltage (PIV) also has an effect on the operation of the half-wave rectifier. The negative half cycle of the input will apply a reverse bias to the diode. The highest value of reverse bias will be at the peak of each negative alternation. The diode must be capable of withstanding this repetitive value of reverse bias.

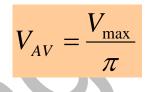

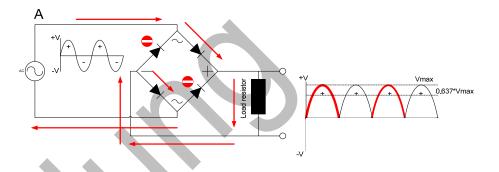

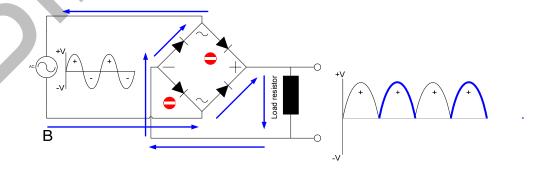

# 1.2.4 Full Wave Rectification

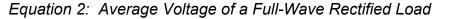

A Full-wave rectifier is a circuit that converts an alternating sine wave into a pulsating DC signal that consists of both halves of a sine wave for each input cycle.

The positive half-cycle of the sine wave is applied at point A (figure 18). The current is forced to the load resistor through the only forward bias diode available at its position. The arrows show the path of the current on the positive half cycle.

Figure 18 The Full Wave Bridge Rectifier Positive Path

The negative half cycle of the sinusoid is applied at point B (figure 19). The arrows show the path of the current on the negative half cycle.

Figure 19 The Fullwave Rectifier Negative Path

The direction of the current through the load is the same for both cycles. Therefore the load signal is DC.

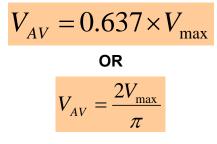

The full period of the applied sinusoid signal is produced at the load resistor. Therefore, the average voltage at the load is twice the value of the half-wave rectified circuit. Equation 2 shows the formulae to calculate the average voltage of a full-wave rectified signal.

Full-wave rectification is more efficient than half-wave rectification because the full cycle of the sine wave is converted to DC. It should be noted, that the DC is still variable. This is undesirable to apply in circuits that require a stable DC supply.

A capacitor can be added across the load resistor to further stabilise the DC output. The addition to the circuit is shown in figure 20.

Figure 20 Capacitor Addition to Bridge Rectifier

It should be noted that the DC output will not be "perfect" (as illustrated). An element of ripple will be evident at the output.

The value of the capacitor will determine the time taken to charge and discharge. The charge/discharge process is the cause of the ripple.

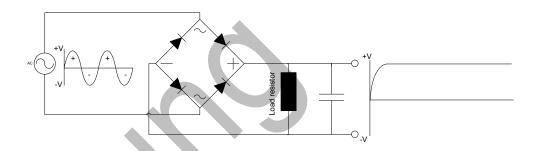

Figure 21 shows the conversion from a full wave rectified DC signal to stable DC. The DC ripple can be minimised by the designer's careful consideration of the capacitor value.

Figure 21 Rectified DC to Stabilised DC

The positive cycle will charge the capacitor until it reaches its maximum value. The voltage of the positive cycle will then decrease. During this time the capacitor will begin to discharge.

Before the capacitor can discharge completely, the negative cycle will re-charge the capacitor to its maximum value. The process will then begin again.

Other methods of full-wave rectification exist for single-phase signals. Methods also exist to rectify three phase signals.

#### 1.2.5 Diode Testing

In most cases, a digital multi-meter (DMM) is the fastest way to check for a defective diode.

A functional diode will show extremely high resistance under reverse bias (or open circuit). It will show very low resistance under forward bias.

## Faulty (Open)

A faulty open diode will read extremely high resistance in both forward and reverse bias. It can be caused by a defective junction on the diode material or an improper connection when mounted to a circuit board. This is the most common type of fault on a diode.

# Faulty (Short)

A short circuit diode will show as zero resistance in both forward and reverse bias.

# **DMM** Testing

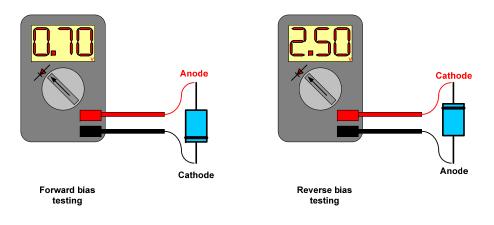

Many digital multi-meters have a continuity function position designed to test the functionality of a diode. It is usually marked by a small diode symbol on the main dial. When this function is in use, the DMM will apply a bias voltage to the diode (Usually 2-3V).

# Figure 22 Functional Diode DMM Testing

# Functioning Diode – DMM Test

The Cathode is marked by a black band on a diode. The red cable (used as positive) should be connected to the Anode to forward bias the diode. The black cable (Ground) should be connected to the Cathode. The user should read between 0.6V -0 .9V (the expected result is 0.7V for silicon). The diode may also emit a loud beep from the speaker when forward biased.

To reverse bias the diode, the user should connect the red wire to the Cathode. The black wire is connected to the Anode. The user should read a voltage based on the DMM supply. For illustrative purposes, 2.5V will be used (shown in figure 22). The DMM may also display 'OL'. These readings indicate a very high path of resistance (very low current = negligible voltage drop).

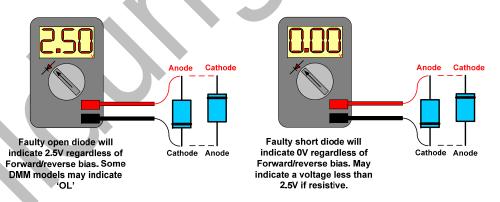

# Defective Diode DMM Test

If a diode has an open circuit fault, the meter will display 2.5V or 'OL' when the diode is both forward and reverse biased. This is shown in figure 23.

Figure 23 Faulty Diode DMM Test

If a diode has a short circuit fault, the DMM will read 0V when forward/reverse biased. The diode may not be a complete short and may exhibit a small internal resistance. This means that it will read a voltage larger than the maximum 0.9V in forward bias, but lower than 2.5V desired in reverse bias (typical values at around 1.1V-1.5V in both directions).

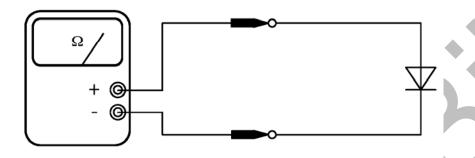

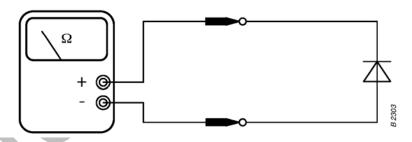

#### **Static Resistance Measurements**

An easy method of testing a diode is to use an ohmmeter. The forward 24 and reverse resistances 25 can be checked at a voltage determined by the battery potential of the ohmmeter and the resistance range at which the meter is set.

#### a) Forward resistance check

Figure 24 Testing a Diode (forward check)

#### b) Reverse resistance check

Figure 25 Testing a Diode (reverse check)

When the test leads of the ohmmeter are connected to the diode, a resistance will be measured that is different from the resistance indicated if the leads are reversed.

The smaller value is called the forward resistance, and the larger value is called the reverse resistance. If the ratio of reverse-to-forward resistance is approximately greater than 10 to 1, the diode should be capable of functioning as a rectifier.

This is a very limited test, which does not take into account the action of the diode at voltages of different magnitudes and frequencies. Tutorial Sheet 2.1: P-N Junction Diodes

- 1. Describe the behaviour of the P-N junction under the following conditions:

- Initial contact (no applied power).

- Forward bias.

- Reverse bias.

- 2a. Demonstrate (with illustrations) the construction of a standard P-N diode in terms of:

- Conventional Current flow.

- P-N junction layout.

- Anode.

- Cathode.

- Equivalent circuit diagram.

- 2b. Describe the main uses of a P-N junction diode?

- 3a. Three Silicon diodes are connected in series with a resistive load ( $R_1$ ) of  $10k\Omega$ . The supply voltage ( $V_S$ ) is 10V. Calculate:

- The Voltage drop across a single diode.

- The Voltage dropped across all three diodes.

- The remaining Voltage across  $R_1(V_{R1})$ .

- The total current draw.

- 3b. Three Silicon diodes are connected in series with a resistive load ( $R_2$ ) of 100 $\Omega$ . The circuit is drawing 29mA of current.

Using ohm's law and known power formulae, calculate:

- The Voltage across the resistor R<sub>2</sub> (V<sub>R2</sub>).

- The Supply voltage (V<sub>S</sub>).

- The Power dissipated in the circuit.

- 4. Three Silicon diodes are connected in parallel. The Supply current is 6A. What is the current through each diode?

- 5a. Draw the circuit diagram of a Half-wave rectifier.

- 5b. Show the output (with respect to the 10V AC input) of a Half-wave rectifying circuit (the barrier potential of the P-N junction must be considered).

- 5c. State the average output Voltage of a 240V Half-wave rectified signal.

- 6a. Draw the circuit diagram of a Full-Wave bridge rectifier.

- 6b. Show the conventional current path of the positive halfcycle of the AC input signal.

- 6c. Show the conventional current path of the negative halfcycle of the AC input signal.

- 6d. Show the output DC signal (with respect to the 10V AC input signal) of a Full-wave rectifier (the barrier potential of a P-N junction must be considered).

.

- 6e. State the average output Voltage of a 240V Full-wave rectified signal.

- 6f. Explain the effect of adding a Capacitor to the Full-wave rectifier circuit.

- 6g. Research and illustrate another type of Full-Wave rectifier circuit using P-N diodes. Explain its operation.

## 1.2.6 Light Emitting Diodes (LEDs)

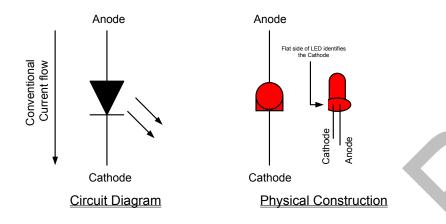

The circuit diagram and physical construction of an LED is shown in figure 26.

Figure 26 Light Emitting Diode (LED)

The forward and reverse conditions of the LED are identical to that of the standard P-N diode.

The exception can be found under the forward bias operation of the LED.

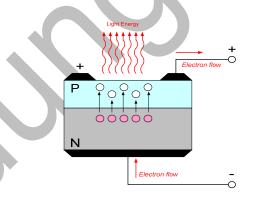

As previously shown, under forward bias conditions, electronhole combinations occur as electrons cross the P-N junction. When the holes and electrons combine, energy is released in the form of heat and light. A large area on a layer of the semi-conductor is left exposed to permit photons to escape as visible light. This process is known as electro-luminescence. This is illustrated in figure 27.

## Figure 27 Electro-Luminescence in a Led

Silicon and Germanium are not used because they primarily produce energy in the form of heat. Gallium Arsenide (GaAs), Gallium Arsenide Phosphide (GaAsP) and Gallium Phosphide (GaP) are used as primary LED semi-conductor materials.

Gallium Arsenide (GaAs) emits infra-red (IR) radiation. Gallium Arsenide Phosphide (GaAsP) emits red or yellow visible light. Gallium Phosphide (Gap) emits red or green light.

The amount of visible light generated is directly proportional to the forward current. The colour of light generated by each material may also be controlled by the doping procedures. A guide to a good operating current to produce sufficient visible light is around 30mA.

A common use for LED's is in seven segment displays and readout displays.

## 1.2.7 Zener Diode

The Zener effect describes the process where a diode's applied voltage reaches a level large enough to allow electrons to break their covalent bonds.

In a standard P-N diode, the leakage current remains constant up to a certain applied reverse bias. When that limit is exceeded the leakage rises to a level that is limited only by circuit resistance/internal impedance.

When operating in forward bias, the Zener diode behaves in an identical fashion to a standard P-N diode. The rush of current can begin when the barrier potential is exceeded.

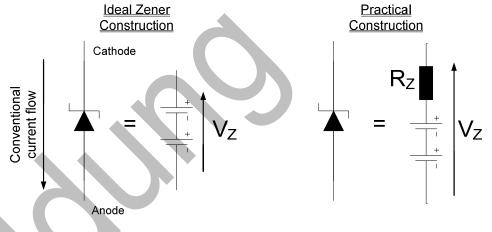

When under reverse bias operating conditions (detailed earlier), a standard P-N diode would be destroyed if the reverse limit is exceeded. The Zener diode can utilise the Avalanche effect. The Zener diode is shown in figure 28.

Figure 28 The Zener Diode

The ideal equivalent circuit shows that if the Zener diode is connected to a varying (unstable) input voltage, it will act as a stable (fixed) signal if the output is taken across it.

The practical circuit shows that the Zener diode has "Internal impedance" due to the manufacture and materials used in the diode construction. This will limit the current through the Zener diode.

The reverse breakdown voltage limit is designed to be lower for a Zener diode ( $3\rightarrow$ 100 Volts) than for a standard P-N diode (Silicon  $\approx$  1000V).

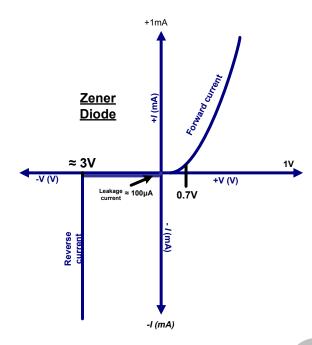

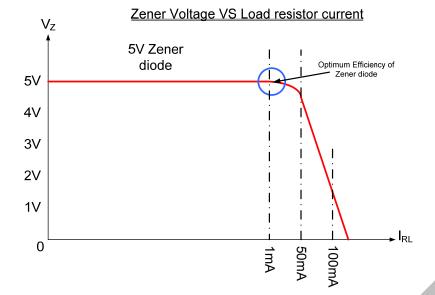

The operating conditions of a Zener diode are shown in figure 29.

## The Zener Diode as a Voltage Stabiliser

$I_{\rm S}$

$V_{S}$

$R_z$

Vn

The Zener diode can be used as a voltage stabiliser. A large reverse current increase can be produced from a small reverse voltage increase.

It is this characteristic that allows a small voltage to be fixed from a larger supply. The design of a Zener diode stabiliser circuit is shown in figure 30.

17

Figure 30 Voltage Stabiliser Circuit

$I_{RL}$

Ζ

$\mathsf{R}_{\mathsf{L}}$

$V_{z}$

Figure 29 Operating Conditions of a Zener Diode

It can be seen from the operating conditions that the "rush of current" behaves the same for the Zener diode when in reverse bias, as it does when in forward bias.

The difference is that the "Rush of current" occurs at a higher value when in reverse bias, than in forward bias. Eg:

- Forward bias potential 0.7V.

- Reverse bias potential 3V→100V.

#### Example:

A 20V stabilised signal is needed from a 50V supply dissipating 4W of power.

This means that the circuit must drop 30V across the series resistor ( $R_S$ ). To calculate the value of the series resistor we must first use the power formula;

$$I_Z = \frac{P_T}{V_Z}$$

Where;

$I_Z$  = Current through the Zener diode  $P_T$ = Power dissipated in the circuit (Watts)  $V_Z$  = Desired Voltage across the Zener diode

So:

$$I_Z = \frac{4W}{20V} = 0.2A = 200mA$$

The current through the Zener diode (therefore the series resistor current) is 200mA.

The series resistor value can now be calculated using ohm's law.

Where;

So:

$V_D$  = Voltage dropped across Series resistor. R<sub>s</sub> = Series resistance.

$R_s = \frac{30V}{0.2A} = 150\Omega$

A 150 $\Omega$  resistor is required to stabilise 20V across a Zener diode from a 50V supply.

Provided the breakdown current is maintained, the Zener can act as a reservoir of current. If the supply voltage increases, the current through the series resistor increases. This maintains the Voltage across the Zener diode.

If the supply falls, the current decreases (with the drop across the resistor), again maintaining the voltage across the diode.

A minimum value of reverse current must be maintained to keep the diode in regulation. This value is known as  $I_{ZK}$ .

The maximum value of reverse current, above which the diode may be damaged, is known as  $I_{\text{ZM}}.$

The data sheet supplied with the diode will detail the Zener test voltage,  $V_{ZT}$ , at a value of reverse current called  $I_{ZT}$ .

The load across a Zener diode should also be observed. It should be noted that current will follow the path of least resistance.

The Zener stabiliser operates more efficiently when its parallel load resistance is a high value.

If the load resistance is allowed to fall, its current will increase (at the expense of the Zener diode). This will mean that the avalanche effect operating the Zener will cease if its voltage falls below the breakdown limit. Equation 5 shows the method of calculating the load current using ohm's law. Equation 6 shows the method of calculating the Zener current using the obtained load current

$$I_{RL} = \frac{V_Z}{R_L}$$

Where;

$I_{RL}$  = Load current.  $V_Z$  = Zener voltage (also equal to load voltage).  $R_L$  = Load resistance.

Equation 5: OhHMs Law used to calcualte Load Current

$$I_Z = I_S - I_{RL}$$

Where;

$I_Z$  = Zener current.  $I_S$  = Total supplied current.

# Equation 6: Zener Current (Calculated From Load Current)

Experimentation on the Zener diode will show that as the Load resistor current increases, the Zener current decreases by the same amount. (The voltage across the Load and Zener will remain fixed if it is above the breakdown limit).

If the load resistor current decreases, the current through the Zener diode will increase by the same amount. Figure 31 shows the effect of lowering the load resistance (increasing load current at the expense of the Zener diode).

## Figure 31 Effect of Lowering Load Resistance

A method to restore the tolerance of the Zener breakdown voltage is to choose a higher series resistor when low-resistance loads are applied across the Zener diode.

A good example application of the Zener diode as a voltage stabiliser is in a circuit designed to protect against Electro-static discharge.

1.2.8 The Shottky Diode

The circuit diagram for a Shottky diode is shown in figure 32.

#### Figure 32 Shottky Diode

The Shottky diode fuses metal to a semiconductor to improve switching speeds for application in logic circuits. The mobility of electrons is greater than holes, so the N-type doped semiconductor is used.

Aluminium has three valance electrons, making it an acceptor atom. When Aluminium is fused to an N-type semiconductor, some of the atoms migrate into the silicon making a very thin Pregion. Almost all of the holes combine with electrons. This means that nearly 100% of the current carriers are electrons as they are abundant in the N-type material.

As a consequence, minority carriers (holes in this case) do not contribute to any current flow process. The diode has a smaller depletion region, thus lower capacitance and a smaller forward conducting barrier voltage (0.2V-0.4V).

#### 1.2.9 Varactor Diode

The circuit diagram for a Varactor diode is shown in figure 33.

Figure 33 Varactor Diode

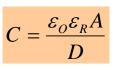

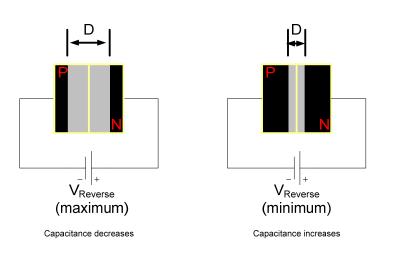

Varactor diodes are known also as variable capacitors. This is because P-N junction capacitance varies with the amount of reverse bias voltage applied to it. This means that the capacitance can be changed simply by changing the reverse bias.

The Varactor diode is mainly used in electronic tuning circuits, such as TV's and radios. It is essentially a reverse bias P-N junction that uses the capacitance of the induced the depletion region. It repels the majority carriers; therefore it will not conduct. This characteristic causes it to behave like the insulating dielectric material of a capacitor (The material between the plates).

The P and N regions are conductive, so they behave like the plates on a capacitor. From module 3 (Capacitors), it can be seen that capacitance is affected by the area of the plates (A), the distance between them (thickness of the dielectric, D) and the dielectric constants ( $\epsilon_0$  and  $\epsilon_R$ ). This is shown in Equation 7.

### Equation 7: Capacitance Formula

As the reverse bias voltage increases, the depletion region at the P-N junction widens. This has the effect of increasing the dielectric thickness which would decrease the value of the capacitor.

As the reverse bias decreases, the depletion region narrows, therefore decreasing the depletion region and increasing the capacitance. This is shown in figure 34.

Figure 34 Depletion Region on a Varactor Diode

The capacitance parameters are generally controlled by the doping methods of the depletion region and the construction of the diode. The Varactor diodes have a typical capacitance range of a few pico-farads to a few hundred pico-farads.

1.2.10 Photo-Diodes

The circuit symbol for a Photo-diode is shown in figure 35.

Figure 35 Photo-Diode

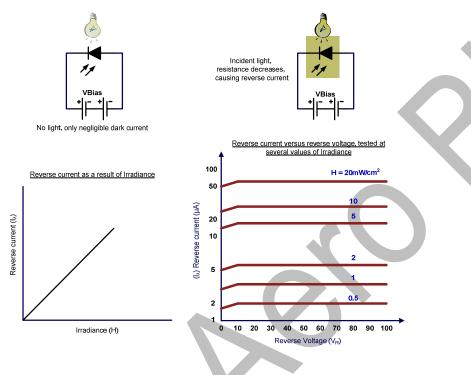

The photo-diode is a P-N junction device that operates in reverse bias. The diode has a transparent area that allows light to strike the junction.

When operating under reverse bias, a standard rectifier diode has a small leakage current caused by minority carriers.

Reverse bias current is generated thermally by electron-hole combinations in the depletion region.

The electron-hole pairs are carried across the junction by the applied reverse bias voltage.

In a rectifier diode, increased electron-hole combinations causes a rise in temperature. This rise in temperature causes a rise in the reverse current.

In a Photo-diode, the reverse current increases with the intensity of light at the exposed P-N junction.

When there is no supplied light, the reverse current  $(I_{\lambda})$  is negligible. This is known as dark current. An increase in light intensity produces an increase in reverse current. Light intensity is expressed in Irradiance (mW/cm<sup>2</sup>). This is shown in figure 40.

Figure 36 Supplied Light on a Photo-Diode

#### 1.2.11 Voltage-Sensitive Components

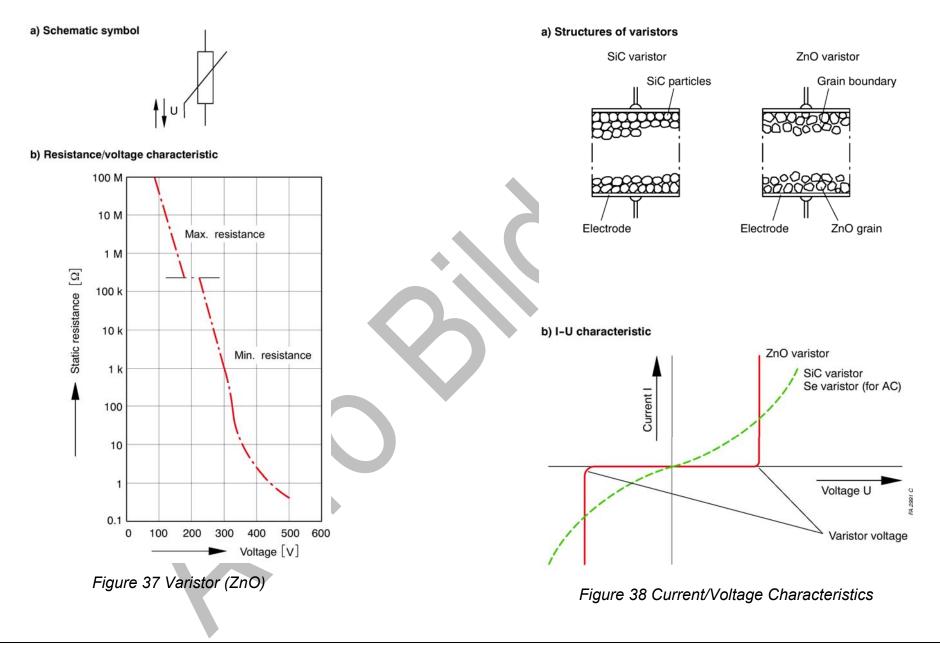

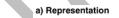

Voltage-sensitive components are referred to as 'varistors'. The name varistor stands for 'variable resistor' but because of its resistance/ voltage characteristic it is also called 'voltage-dependent resistor' (VDR). Detail a) shows the schematic symbol of a VDR.

As shown in the resistance/voltage characteristic diagram (detail b)), the resistance of a VDR decreases when the applied voltage increases, and the resistance increases when the voltage decreases. This characteristic makes the VDR an appropriate component to absorb transient voltages occurring in electronic circuits.

Varistors are solid-state components made from semiconductor materials, such as silicon carbide (SiC), selenium (Se) and zinc oxide (ZnO) as main ingredients Figure 38, detail a)).

The semiconductor material greatly used determines the voltagedependent characteristic and the ability of the VDR to absorb transient voltages (detail b)).

Generally, the insulation between SiC particles (in case of SiC varistors), and those of ZnO grains (in case of ZnO varistors) is maintained while the voltage applied to varistors is low. But, when a voltage beyond a specified voltage value (the varistor voltage) has been applied, it destroys the insulation and causes a large current flow, that means the resistance becomes low. The insulation is restored when current flow sharply decreases and the applied voltage falls below the varistor voltage value.

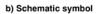

#### 1.2.12 Photo -Conductive Cells

Photo conductive cells, commonly known as light-dependent-resistors (LDR), are passive electronic components used for the detection of light (optoelectronic radiation). They consist of semiconductor material, such as

- $\Box$  cadmium sulphide (CdS)

- $\Box$  cadmium selenide (CdSe)

- □ lead sulphide (PbS).

In Figure 39, detail a) a photo-conductive-cell is represented. Detail b) shows the schematic symbol.

Photo-conductive-cells can be regarded as resistors which change their resistance according to the intensity of light illumination (detail c). The photo-conductive resistance decreases when the light intensity increases, and vice versa, when the light intensity decreases the resistance increases. Since photo-conductive cells have no PN junctions, they can be used for DC and AC circuits. They provide high photo-sensitivity to light, employing wavelengths from ultraviolet to infrared.

These types of optoelectronic detectors are

- □ highly sensitive to light radiation

- □ robust

- □ cheap, compared to other optoelectronic detectors.

## **Application of Photo -Conductive Cells**

Generally, photo conductive cells are employed in electronic circuits as

- □ dimming switches

- □ automatic flame -guards

- □ lighting control

- photometers.

#### c) Characteristic diagram

Figure 39 Photo-Conductive Cell

### 1.2.13 Thyristor

Thyristors are constructed using four separate layers of semiconductor material. They are called the Silicon Controlled Rectifier (SCR).

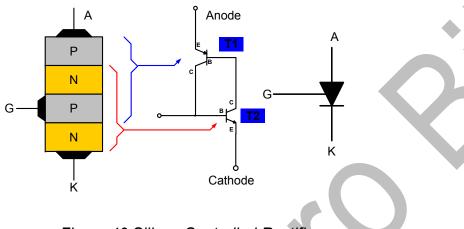

The construction, equivalent circuit and circuit symbol are shown in figure 40.

Figure 40 Silicon Controlled Rectifier

The physical construction of the SCR is thought of as an NPN transistor interconnected with a PNP transistor. It has two P regions and two N regions. The two middle layers of the transistor are shared.

The SCR is a Uni-directional device (like a rectifier diode) with three terminals. The current conduction is controlled by the gate (G). Normal forward bias operation applies when a positive voltage is applied to the gate.

Normal transistor operation is covered later in these notes. When a burst of current is applied to the gate, it becomes the initial base of the transistor junction **T2**. This action switches **T2** on; pulling a larger current from the collector to the emitter (this is the normal behaviour of an NPN transistor).

This also has an effect on the PNP transistor, illustrated as **T1**. The base of **T1** is connected to the collector of **T2**. The large current flow into the collector of **T2** forms the conducting path for the base current of **T1**. This action switches **T1** on, allowing current to flow from the emitter into the base. In turn, **T2** pulls a larger current from the collector of **T1** into its base.

The entire SCR diode current sustains itself as the collector current of **T1** is large enough to support the base current of **T2**, even when the gate voltage is removed. This base current is the minimum required value to keep **T2** switched on. This becomes the minimum holding current.

The SCR will remain switched on until the electron flow from the Cathode to the Anode (Conventional current flow of Anode-Cathode) is greater than or equal to a specified holding current. Once the active current drops below the holding value, the SCR will turn off. It can be switched on again with another voltage applied to the gate.

The SCR will also switch off if a reverse bias is applied to the diode or the supply is removed completely.

The diagram in figure 41 shows the SCR used to rectify and control the average power delivered to a load. It will half-wave rectify a sinusoidal load like a normal diode. A trigger pulse is applied to the SCR gate during the positive half-cycle of the input signal. If the SCR is triggered earlier in the half-cycle, the load receives more average power. If the SCR is triggered later in the half-cycle, less average power is delivered to the load.

#### 1.2.14 The Triac

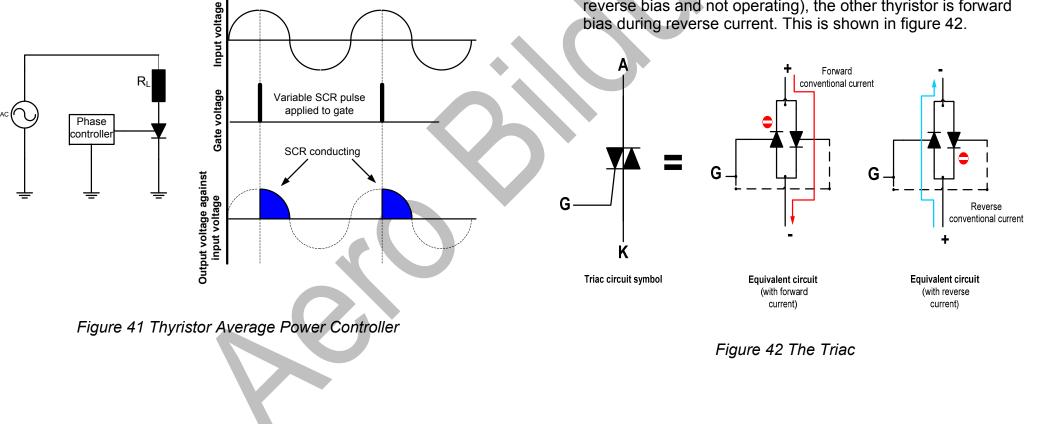

The Triac consists of two Tyristors connected to allow bidirectional current flow. Both thyristors share a common gate. The circuit symbol for a Triac is shown in figure 42.

The simplest method of describing the Triac shows one thyristor is forward bias during forward current (the other is reverse bias and not operating), the other thyristor is forward bias during reverse current. This is shown in figure 42.

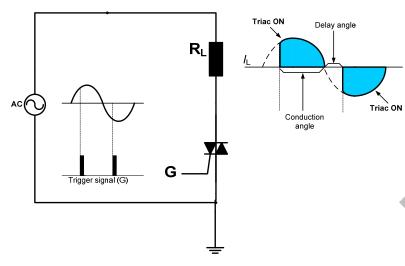

Triacs can also be used to control the amount of active power delivered to a load using the same method as the thyristor. The gate trigger can be applied to deliver a controlled portion of each half-cycle (both positive and negative) to the load. The diagram for the full wave power controller is shown in figure 43.

Figure 43 Full Wave Phase Controller

Throughout the positive half-cycle of the input, the diode is off until the gate is triggered. This is known as the delay angle. When this occurs the diode is allowed to conduct for the remaining portion of the half-cycle. This is known as the conduction angle.

The Triac is bi-directional, so a reverse current is allowed through the diode. This means that the triggered phase angle control can also be applied to the negative half-cycle of the input.

### 1.2.15 The Diac

The Diac is a bi-directional device that operates without a gate. It can operate if a sufficient voltage, known as the break-over potential, is applied across it. The circuit symbol for the Diac is shown in figure 44.

Figure 44 The Diac

#### 1.2.16 Tutorial Sheet 2.2: Other Diodes

- 1a. Show the circuit diagram of an LED, include the conventional current flow.

- 1b. What is the cause of emitted light in an LED?

- 1c. What Semi-conductors are used in the construction of an LED?

- 2a. A Zener diode exhibits a 50mV change in V<sub>z</sub> for a 2mA change in I<sub>z</sub>. What is the Zener impedance?

- 2b. A certain Zener diode has an impedance of 5 $\Omega$ . The data sheet supplied with the diode gives V<sub>ZT</sub> = 6.8V at I<sub>ZT</sub> = 20mA.

What is the voltage across the Zener diode,  $V_Z$ , when the current is 30mA?

What is the  $V_Z$  when  $I_Z = 10$ mA?

2c. Use figure 34 as a circuit design, the load resistor ( $R_L$ ) can be ignored. Determine the minimum and maximum voltages that can be regulated by the Zener diode if the minimum operating current,  $I_{ZK} = 1mA$ ,  $V_{ZT} = 5.1V$  at  $I_{ZT} = 7mA$  and the maximum operating current,  $I_{ZM} = 15mA$ .

The Zener impedance is 10  $\Omega$ . The series resistor,  $R_Z$  is 680  $\Omega$ .

2d. Use figure 34 as a circuit design. Determine the minimum and maximum load currents for which the Zener diode will maintain regulation.

The supply voltage is 24V. The series resistor  $R_Z$  is 470 $\Omega$ .  $V_Z$  = 12V,  $I_{ZK}$  = 3mA,  $I_{ZM}$  = 90mA.

Assume that  $Z_z = 0\Omega$  and  $V_z$  remains a constant 12V over a range of current values for simplicity. What is the minimum  $R_L$  that can be used?

- 3a. Name the three types of Thyristor.

- 3b. Describe the operation of one of the three Thyristors.

- 4. Describe the operation of the Schottky diode.

- 5. Describe the operation of the Varacter diode.

- 6. Describe the operation of the Photo-diode.

#### **Tutorial Sheet 2.1 Solutions**

- 1. Directly referenced from the text.

- 2a. Directly referenced from the text.

- 2b. Directly referenced from the text.

- 3a. The voltage drop across a single diode is 0.7V. The voltage drop across all 3 diodes is 2.1V (0.7V\*3). The remaining voltage across  $R_1$  is;

$$V_{R1} = V_S - (3 \times V_D)$$

so;

$V_{R1} = 10V - 2.1V = 7.9V$

The current draw from the supply is;

$$I_{s} = \frac{VR_{1}}{R_{1}} = \frac{7.9V}{10k\Omega} = 790\,\mu A$$

3b. The voltage across the resistor,  $R_2$ , is developed using the supply current;

$$V_{R2} = 29mA \times 100\Omega = 2.9V$$

The supply voltage is determined using the calculated drop across  $R_2$  and the drop across the 3 diodes.

$$V_{s} = V_{R2} + (3 \times V_{D})$$

$$V_{s} = 2.9V + (3 \times 0.7V)$$

$$V_{s} = 2.9V + 2.1V = 5V$$

The total power dissipated in the circuit is;

$$P_T = V_S \times I_S = 5V \times 29mA = 145mW$$

4. The three diodes are in parallel so the current will divide equally between them;

$$I_D = \frac{I_T}{3} = \frac{6A}{3} = 2A$$

- 5a. Directly referenced from the text.

- 5b. Directly referenced from the text.

- 5c. The average value of a 240V Half-wave rectified AC signal is;

$V_{AV} = 0.318 \times V_{max}$  $V_{AV} = 0.318 \times 240V = 76.32V$

- 6a. Directly referenced from the text.

- 6b. Directly referenced from the text.

- 6c. Directly referenced from the text.

- 6d. Directly referenced from the text.

- 6e. The average voltage of a 240V full-wave rectified signal is;

$V_{AV} = 0.637 \times V_{max}$  $V_{AV} = 0.637 \times 240v = 152.88V$

- 6f. Directly referenced from the text.

- 6g. Personal research.

The desired clamping frequency is;

$$F_{CLAMP} = 10F_{RC}$$

$$F_{CLAMP} = 10 \times 10Hz = 100Hz$$

#### **Tutorial Sheet 2.2: Solutions**

- 1a Directly referenced from the text.

- 1b. Directly referenced from the text.

- 1c. Directly referenced from the text.

- 2a.  $Z_z = \frac{\Delta V_z}{\Delta I_z} = \frac{50mV}{2mA} = 25\Omega$ , the term ' $\Delta$ ' denotes the change in signal values.

- 2b. Figure 11a can be used from the text. The 30mA current is a 10mA increase ( $\Delta I_Z$ ) above  $I_{ZT}$  = 20mA.

So;

$$\Delta I_z = +10 mA$$

Meaning;

$$\Delta V_{Z} = (\Delta I_{Z} \times Z_{Z}) = (10mA) \times (5\Omega) = +50mV$$

The change in voltage due to the increase in current above the  $I_{ZT}$  value causes the Zener terminal voltage to increase. The Zener voltage for  $I_Z$  = 30mA is;

$$V_{Z} = 6.8V + \Delta V_{Z} = 6.8V + 50mV = 6.85V$$

The Zener voltage for  $I_Z$  = 10mA can also be given. The 10mA current is a 10mA decrease below  $I_{ZT}$  = 20mA.

So;

$\Delta I_z = -10mA$

Meaning

$$\Delta V_{z} = (\Delta I_{z} \times Z_{z}) = (-10mA) \times (5\Omega) = -50mV$$

The change in Zener voltage due to the decrease in current below  $I_{ZT}$  causes the Zener terminal voltage to decrease. The Zener voltage for  $I_Z$  = 10mA is;

$$z = 6.8V - \Delta V_z = 6.8V - 50mV = 6.75V$$

2c. Using figure 11c as a design, with the Zener impedance at  $10\Omega$  and a  $680\Omega$  series resistor;

At  $I_{ZK}$ , the output voltage is;

$$V_{OUT} = V_{ZT} - \Delta V_Z$$

so;

$$V_{OUT} = 5.1V - (\Delta I_Z \times Z_Z)$$

The value of  $V_{ZT}$  at  $I_{ZT}$  has been given so it can be assumed that these will be the normal operating values. This means that the value of  $I_{ZT}$  must change to  $I_{ZK}$ . This means that the Zener current will change from 7mA ( $I_{ZT}$ ) to 1mA ( $I_{ZK}$ ). This can be considered as shown;

$$V_{OUT} = 5.1V - ((I_{ZT} - I_{ZK}) \times Z_Z)$$

so;

$$V_{OUT} = 5.1V - ((6mA) \times 10\Omega)$$

finally

$$V_{OUT} = 5.1V - 0.06V = 5.04V$$

The minimum input voltage can be determined;

$$V_{IN(\min)} = (I_{ZK} \times R_Z) + V_{OUT}$$

so;

$V_{IN(\min)} = ((1mA)(680\Omega)) + 5.04V = 5.72V$

At  $I_{ZK}$ , the change in Zener current is

15mA - 7mA = 8mA, so the maximum output voltage is;

$$V_{OUT} = 5.1V + \Delta V_Z$$

so;

$$V_{OUT} = 5.1V + (\Delta_{IZ} \times Z_Z)$$

so;

$$V_{OUT} = 5.1V + ((8mA) \times (10\Omega))$$

finally

$$V_{OUT} = 5.1V + 0.08V = 5.18V$$

The maximum input voltage can now be calculated;

$$V_{IN(\text{max})} = (I_{ZM} \times R_Z) + V_{OUT}$$

so;

$$V_{IN(\max)} = ((15mA)(680\Omega)) + 5.18V = 15.38V$$

2d. When  $I_L = 0A$ ,  $I_Z$  is at its maximum.  $I_Z$  is also the total circuit current ( $I_T$ ) in this condition.

$$I_{Z} = \frac{V_{IN} - V_{Z}}{R_{Z}} = \frac{24V - 12V}{470\Omega} = 25.5mA$$

This is significantly less than the maximum operating current,  $I_{ZM}$ , at 90mA, so it is acceptable to use. The minimum operating load current through  $R_L$  is 0A ( $I_{L(min)} = 0A$ ).

The maximum value of  $I_L$  will occur through  $R_L$  when  $I_Z$  is at its minimum (equal to  $I_{ZK}$ ). This means that  $I_{L(max)}$  is determined as follows;

$$I_{L(\text{max})} = I_T - I_{Z(\text{min})} = 25.5mA - 3mA = 22.5mA$$

The minimum value of R<sub>L</sub> must be;

$$R_{L(\text{min})} = \frac{V_Z}{I_{L(\text{max})}} = \frac{12V}{22.5mA} = 533\Omega$$

- 3a. Directly referenced from the text.

- 3b. Directly referenced from the text.

- 4. Directly referenced from the text.

- 5. Directly referenced from the text.

- 6. Directly referenced from the text.

## 1.3 TRANSISTORS

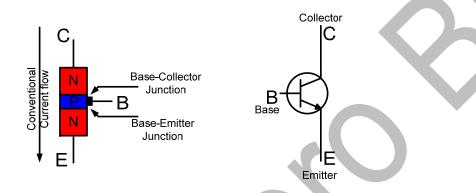

## 1.3.1 The NPN Transistor

A transistor is a semi-conductive device used for amplification and automatic/digital switching.

The Bi-polar transistor crystal is constructed using two P-N junctions.

The construction of an NPN transistor is shown in figure 45.

Figure 45 NPN Transistor Construction

Electrons are the majority carrier in the NPN transistor. The inner "P" region (known as the base) is thinner and very lightly doped in comparison to the "N" regions. The arrow from the device indicates the direction of conventional current flow.

#### NPN Characteristics

For the transistor to be on, the Base-Emitter junction must be forward biased. Much like the diode, the B-E junction must have a forward potential of at least 0.7V if it is a silicon device.

The base-emitter junction allows electron-hole combinations when operating in forward bias. This current is small (negligible) due to doping levels in the base and emitter regions. The thin base (P) region has a limited number of available holes when compared to the significant number of free electrons that have been applied to the Emitter. The remaining free electrons are attracted to the Collector supply voltage so they diffuse over the B-C junction.

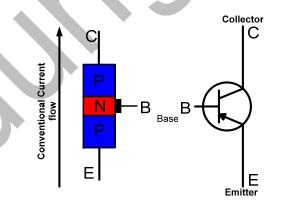

Figure 46 shows the electron flow in the NPN transistor for illustrative purposes. It should be noted that conventional current flow is in the exact opposite direction to electron flow.

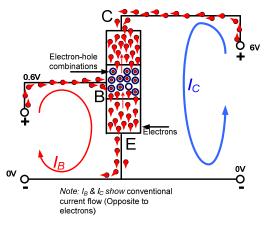

Figure 46 Electron Flow in an NPN Junction

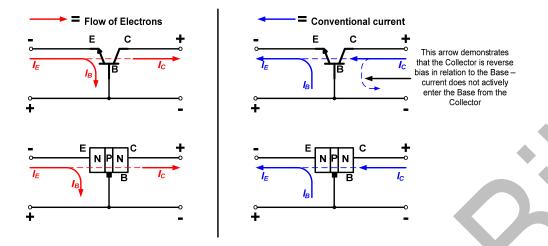

The Base-emitter junction is forward bias in relation to the Base. The Base-Collector junction is reverse bias in relation to the Base. This is shown in figure 47.

The small conventional current flow in the B-E junction "pulls" a much larger current from the Collector. This is because the Base-Emitter combinations cross into the more heavily doped (N-type) Collector.

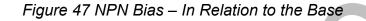

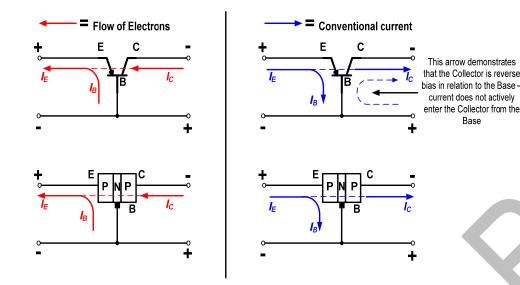

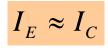

Consequently, a small change in Base current  $(I_B)$  causes a larger change in Collector current  $(I_C)$ . The ratio of Collector current to Base current is known as 'B'. Equation 1 shows the method of calculating the value of B.

The ratio may also be referred to as  $H_{FE}$  in some Electronic texts. The value of B is also sensitive to temperature. If the temperature is constant, the value of B is directly related to  $I_C$ . If the temperature is increased, the value of B will also increase. If the temperature is decreased, the value of B will also decrease.

It can also be seen that the conventional current output of the transistor is the Emitter ( $I_E$ ). The Emitter current is the sum of the Base and Collector currents. Equation 2 shows the method of calculating the **actual** emitter current.

$$I_E = I_C + I_B$$

Equation 2: Method of Calculating Emitter Current  $(I_E)$

Figure 48 shows the conventional current flow of an NPN transistor.

Figure 48 Conventional Current Flow of an NPN Transistor

1.3.2 The PNP Transistor

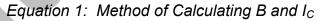

The construction of a PNP transistor is shown in figure 49.

Figure 49 PNP Transistor Construction

As with the NPN transistor, the Base-Emitter junction must operate under forward bias to be active. To operate under this condition with Silicon, the bias must exceed 0.7V. Holes are the majority carriers in the PNP transistor.

The Emitter is still forward biased with respect to the base. However, in the case of the PNP transistor, the Emitter must be at a higher voltage than the Base (NPN transistor has the Base at a higher voltage than the Emitter). The Collector is still reverse biased with respect to the Base. The Collector must be at a lower voltage than the Base. This is shown in figure 50.

Figure 50 PNP Bias in Relation to the Base

Figure 51 shows the Conventional current flow in a PNP transistor.

Figure 51 Conventional Current Flow in a PNP Transistor

It can be seen from the conventional current input to the PNP transistor that the Base and Collector currents are equal to the Emitter current when added together. The method of calculating the Emitter current is as shown in Equation 2.

$$I_E = I_C + I_B$$

Equation 2: Method of Calculating Emitter Current  $(I_E)$

Base

#### 1.3.3 Gain

Gain is the measured amount that an electrical signal is increased or decreased. It is used to measure the level of amplification. This gain value is generated from the ratio of the output to the input.

Attenuation is used to describe loss from an electrical output signal (in relation to the input). In these circumstances the ratio of output to input is less than '1'.

Gain and Attenuation is a useful method of calculating the effectiveness of an amplifier. The primary objective of amplification is to produce a larger voltage/current/power signal from a smaller signal. The circuit symbol for an amplifier is shown in figure 3a.

This equation is used to generate the commercial unit of gain. This is measured in the Decibel (dB) unit. The equation to convert the gain ratio in Decibels is shown in equation 3b.

$A_{\nu}(dB) = 20\log_{10}(G)$

Equation 3b: Gain in dB

Figure 52 Circuit Symbol of a Standard Amplifier

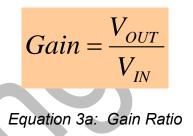

The ratio of a single amplifier is simply the output voltage (AC) divided by the input voltage (AC). Due to the fact that this is a ratio, there are no units. This is shown in equation 3a.

#### Example:

A Voltage amplifier has an AC input of 0.2V. It has an output of 5V. To calculate the gain ratio.

$$Gain = \frac{V_{OUT}}{V_{IN}} = \frac{5V}{0.2v} = 25$$

This amplifier has a gain ratio of 25. This means that the output is 25 times larger than the input. This can now be converted to dB.

$$A_{v}(dB) = 20\log_{10}(25) = 27.95dB$$

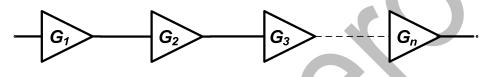

This is useful when many amplifiers are cascaded in series to create a multi-stage amplifier. A multi-stage amplifier is shown in figure 3b. The character ' $G_n$ ' represents the number of amplifiers.

Figure 3b: Multi-Stage Amplifier

The total gain ratio is the product of all the amplifiers. This is shown in equation 3c. This means that the gain in dB is the sum of all the amplifiers dB values. This is shown in equation 3d.

$$G_{TOTAL} = G_1 \times G_2 \times G_3 \times \dots G_n$$

Equation 3c: Multi-Stage Amp Total Gain

$A_{v(TOTAL)}(dB) = A_{v}1(dB) + A_{v}2(dB) + A_{v}3(dB)....A_{v}n(dB)$

Example:

A cascaded amplifier has the following gains.

$G_V 1$  = 10,  $G_V 2$  = 15 and  $G_V 3$  = 20. The overall gain ratio can be calculated as shown.

$$G_{TOTAL} = 10 \times 15 \times 20 = 3000$$

The gain in dB is calculated as shown for each stage and in total.

$$A_{v}1 = 20 \log_{10}(10) = 20 dB$$

$$A_{v}2 = 20 \log_{10}(15) = 23.5 dB$$

$$A_{v}3 = 20 \log_{10}(20) = 26 dB$$

$A_{\nu(Total)} = 20dB + 23.5dB + 26dB = 69.5dB$

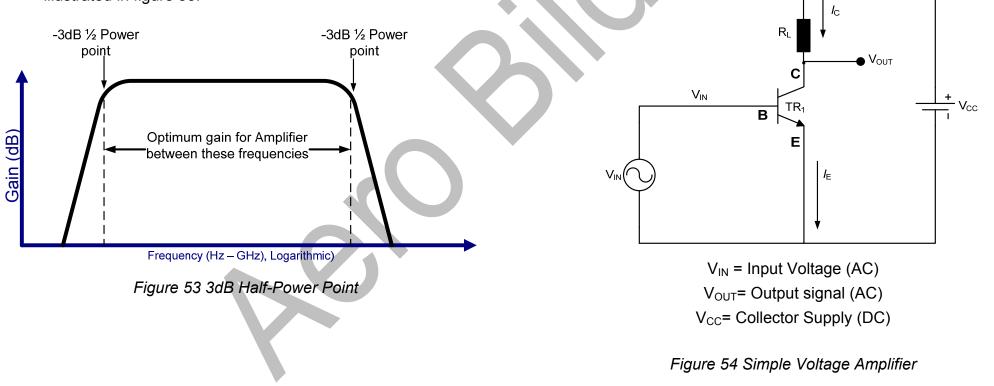

The gain behaviour of an amplifier is very sensitive to frequency, so the gain (dB) is used when calculating the best frequency to operate an amplifier.

The frequency boundaries for the best gain are measured at 3 decibels down from the desired operating gain. This is used when calculating the system bandwidth. The 3dB 'down-point' is the point at which the system consumes half the power that it would if it was running at the desired gain value. This is illustrated in figure 53.

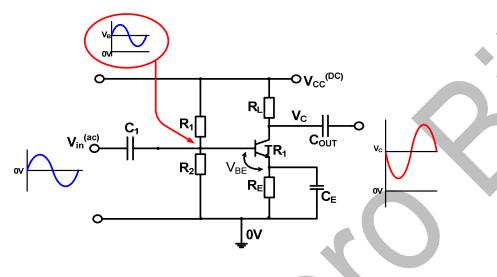

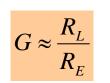

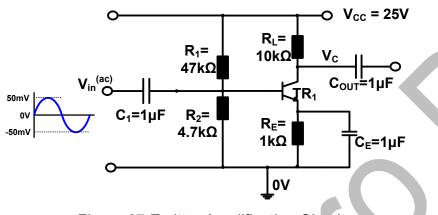

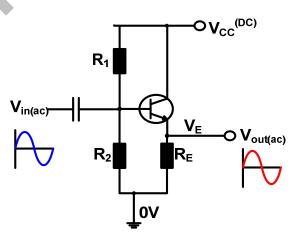

## 1.3.4 THE TRANSISTOR AS A VOLTAGE AMPLIFIER

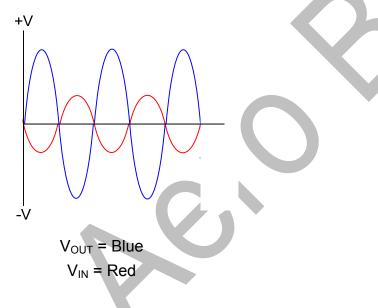

DC bias allows a transistor to operate as an amplifier. The circuit describes a current amplifier. This can be converted to a Voltage amplifier with a simple adjustment.

To obtain an output voltage, a load resistor must be added in series with the collector of the transistor. Figure 54 shows the transistor when converted to a simple voltage amplifier.

The base-collector junction is already very high resistance (Kilo-Ohms) because it operates in reverse bias (with respect to the base, as described earlier). That means that the addition of a few hundred Ohms' resistance will have little overall effect on the Collector current.

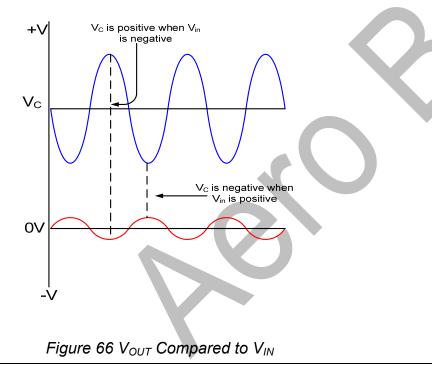

If an AC signal voltage is applied, it will cause an AC signal current at the Collector of the transistor. The addition of a series resistor will convert that Collector current to a Collector voltage.

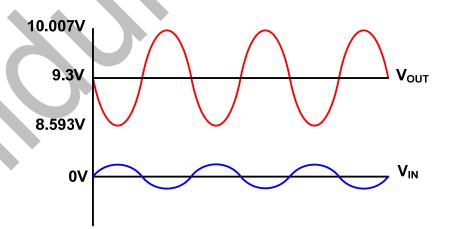

The application of a load will cause the output voltage ( $V_{OUT}$ ) to appear in opposite polarity to the input voltage ( $V_{IN}$ ). The output signal is shown in comparison to the input signal is shown in figure 55.

It should be noted that figure 55 is for illustrative purposes. The signal ' $V_{OUT}$ ' will be much larger in comparison than the signal ' $V_{IN}$ '. This is due to the gain of the transistor. There will also be a DC offset to  $V_{OUT}$  determined by the DC voltage drop across  $R_L$ . It should be noted that the voltage drop across  $R_L$  is calculated using ohm's law ( $V_{RL} = I_C \times R_L$ ).

## DC Bias Applied to a Voltage Amplifier

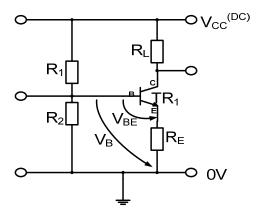

A potential divider network is used to control the bias to the Base of the transistor. This bias allows current to flow into the Base and generate current carriers to the Emitter. Figure 56 shows the divider-controlled voltage amplifier.

Figure 56 Potential Divider Network

Figure 55 V<sub>OUT</sub> Compared to V<sub>IN</sub>

The use of the PD network ensures that two supplies are not required to create the Collector supply and the Base bias. (The Base-Collector region requires a supply. The Base-Emitter also requires a supply). This would not be practical for circuits with multiple transistors.

## $R_1$ and $R_2$

These resistors are used to form a potential divider network from the main supply rail. They create the bias voltage to the Base of the transistor.

The Base voltage (V<sub>B</sub>) is the same as the voltage across V<sub>R2</sub>. The values of resistors R<sub>1</sub> and R<sub>2</sub> determine V<sub>R2</sub> and V<sub>B</sub>. It should be noted that Base voltage (V<sub>B</sub>) is not always equal to V<sub>BE</sub>. V<sub>BE</sub> is the Base-Emitter voltage. V<sub>BE</sub> is fixed at 0.7V.

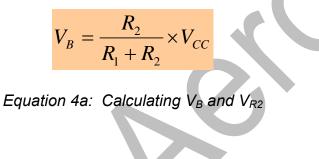

The Base voltage ( $V_B$  and hence  $V_{R2}$ ) can be calculated using equation 4a. Figure 57 proves that the ratio of resistor values controls the Base voltage.

## Figure 57 PD Ratio Effect on V<sub>B</sub>

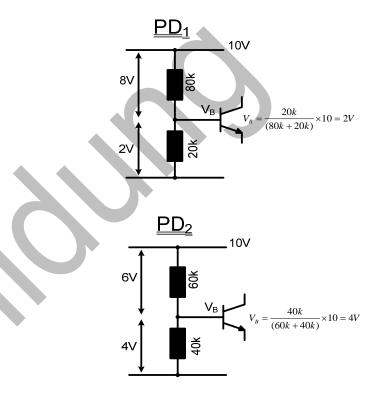

The diagram PD<sub>1</sub> shows the Base voltage (V<sub>B</sub>) with resistor values of  $80k\Omega$  (R<sub>1</sub>) and  $20k\Omega$  (R<sub>2</sub>). The DC supply (V<sub>CC</sub>) is 10V. The voltage across R<sub>1</sub> is shown to be 8V. The voltage across R<sub>2</sub> (therefore V<sub>B</sub>) is 2V.

The diagram PD<sub>2</sub> shows the Base voltage (V<sub>B</sub>) when the resistor values of the potential divider have been changed to  $60k\Omega$  (R<sub>1</sub>) and  $40k\Omega$  (R<sub>2</sub>). The Base voltage is now shown to be 4V.

When the exact voltage drop across  $R_1$  is known, the Base current can be calculated using ohm's law. Equation 4b shows how to calculate the current into the Base ( $I_B$ ).

$I_B = I_{R1} - I_{R2}$

## Emitter Resistor (R<sub>E</sub>) (Temperature stabilisation)

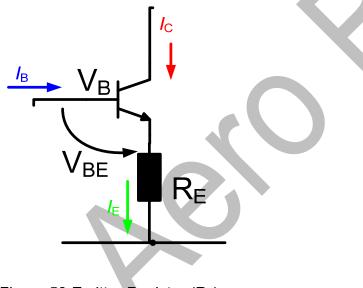

The resistor  $R_E$  is used to prevent the Emitter from overheating. This prevents thermal runaway. Figure 58 shows the Emitter resistor.

Figure 58 Emitter Resistor ( $R_E$ )

The voltage across  $R_E$  can be calculated using  $V_B$  and  $V_{BE}$  (fixed at 0.7V). Equation 4c shows the method of calculating the Emitter voltage ( $V_{RE}$ ).

$$V_{RE} = V_B - V_{BE}$$

The Emitter current ( $I_E$ ) can be calculated (from ohm's law) if the Base and Collector currents ( $I_B$  and  $I_C$ ) are not known. This method is shown in equation 4d.

Equation 4d: Emitter Current (*I<sub>E</sub>*)

It can also be seen that Base current ( $\mu$ A) is negligible when compared to Collector current (mA). For analysis purposes, it can be assumed that Emitter current ( $I_E$ ) is approximately equal to Collector current ( $I_C$ ). Equation 4e shows the method to determine the approximate collector current.

Equation 4e: Approximate Collector Current

## **Collector Characteristics**

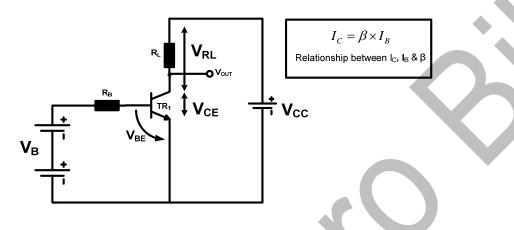

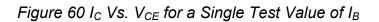

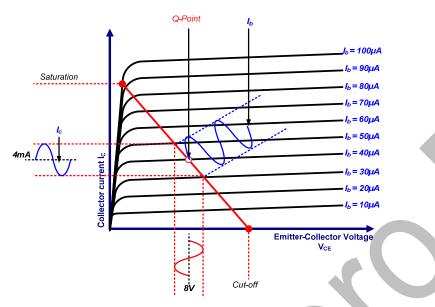

The simple amplifier circuit can be used to test for Collector characteristics. The objective is to show how the Collector current ( $I_C$ ) varies with changes to the Collector-Emitter voltage ( $V_{CE}$ ).

These changes in  $V_{CE}$  can be conducted for fixed levels of Base current,  $I_B$ . This is shown in figure 59.

Figure 59 Simple Amplifier with Fixed Base Current

If the Base voltage ( $V_B$ ) is fixed to generate a specific level of Base current and the Collector supply ( $V_{CC}$ ) is fixed to zero, the Base-Emitter junction is forward biased (0.7V). The Emitter and Collector are both 0V, meaning the Collector is now forward biased with respect to the Base (this is because the Base is at a higher potential than the Collector). The Base current conducts through the Base-Emitter junction (B-E) due to the low resistance path to ground. The Collector is 0V, causing  $I_C$  to be zero.

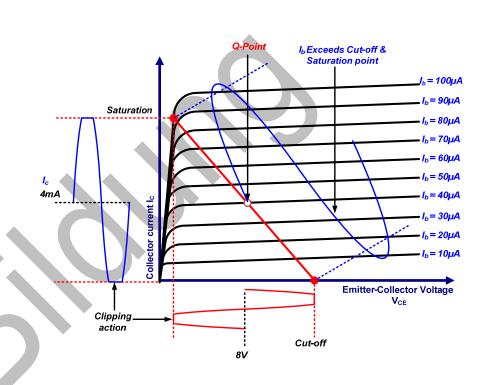

When both junctions are forward biased, the transistor is in the 'Saturation' region. This is shown on point  $A \rightarrow B$  on figure 60.

If V<sub>CC</sub> increases, the Collector current increases. As a consequence, V<sub>CE</sub> also gradually increases. The Base-Collector junction is still forward biased because V<sub>CE</sub> is less than the Base-Emitter voltage (V<sub>BE</sub> = 0.7V).

Under ideal conditions, the Transistor will enter the 'Active' operation (also known as linear) when  $V_{CE}$  exceeds 0.7V. This is because the B-C junction has become reverse biased (The Base is now at a lower potential than the Collector).

Once the B-C junction becomes reverse biased, the Collector current can remain relatively constant, even as  $V_{CE}$  continues to increase.  $I_C$  will remain constant provided  $I_B$  and the load resistor  $R_L$  do not change.

The Collector current will not be exactly constant. It will actually increase slightly with an increase in  $V_{CE}$ .

This occurs because the Base-Collector depletion region widens (due to normal reverse bias operation). There are fewer holes in the Base for electron-hole pairs. This causes an increase in the Collector/Base gain (B). Equation 1 (shown earlier) shows the relationship between Collector and Base currents. The 'Active' region is shown between points  $B \rightarrow C$  on figure 60. This region is used to carry out transistor amplification.

Once the V<sub>CE</sub> voltage reaches a sufficiently high value, the reverse biased B-C junction begins to breakdown. The Collector current rapidly increases. This is shown between points C $\rightarrow$ D on figure 60. Operation in the 'Breakdown' region would cause catastrophic destruction to the transistor.

The collector current characteristic curves can be plotted for many different values of  $I_B$ . This is illustrated in figure 61.

Figure 61 I<sub>C</sub> Vs. V<sub>CE</sub> for Multiple Values of I<sub>B</sub>

## **Cut-off Considerations**

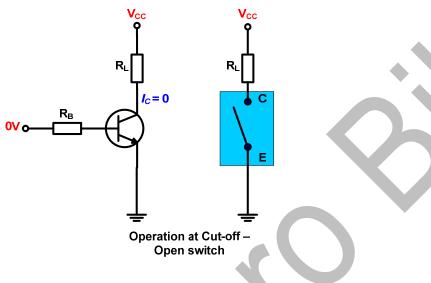

The transistor is operating in the Cut-off region when  $I_B = 0$ . When this occurs no real amplification can take place. It should be noted that a negligible leakage current is generated from the Collector. This is mainly caused by thermally produced carriers. This value can be known as  $I_{CEO}$ . This has been exaggerated in figure 61 for illustrative purposes. Under Cut-off conditions, both the B-E junction and the B-C junction are reverse biased.

The Cut-off value is defined as the 'non-conducting' state of a transistor.

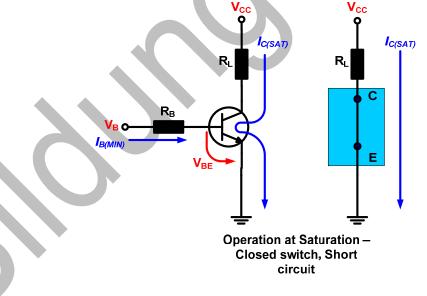

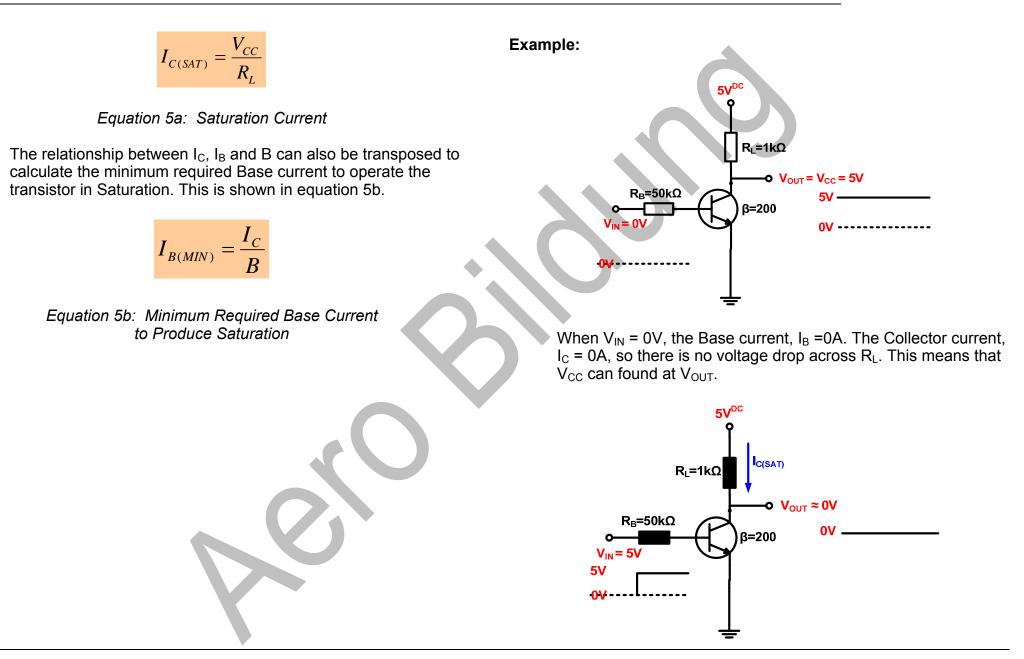

#### **Saturation Considerations**

Saturation is the state of a Bi-polar junction transistor in which the Collector current has reached a maximum value and is independent of a further increase in Base current.

Under Saturation conditions,  $I_C$  increases as  $I_B$  increases. The voltage drop across  $R_L$  increases, causing  $V_{CE}$  to decrease.

$V_{CE}$  eventually drops to the saturation value, known as  $V_{CE(SAT)}$ . At this point,  $I_C$  cannot increase further, even with an increase in  $I_B$ . The relationship between  $I_C$ ,  $I_B$  and B (equation 1) becomes invalid.  $V_{CE(SAT)}$  usually occurs below the 'knee' of the Collector curve. It is a negligible value (assumed to be 0V).

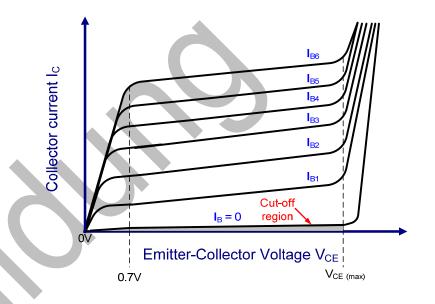

#### Quiescence (Q-Point)

The Q-point is used to determine the  $I_C$  and  $V_{CE}$  values for any given Base current.

The Base current is established using the Base voltage as a bias. A 'DC load-line' can be drawn onto the transistor characteristic curve. It is described as the point where the Base current curve intersects the DC load line. The co-ordinates of the Q-point are the values of  $I_C$  and  $V_{CE}$ . This is shown in figure 62.

Figure 62 Quiescent Point Using a Load-Line

The load-line is determined by  $R_L$  and  $V_{CC}$ , not the transistor in use. A straight line is drawn between the Saturation and Cut-off regions of the Collector curve. Any value of  $I_C$  and its  $V_{CE}$  value will operate on this line.

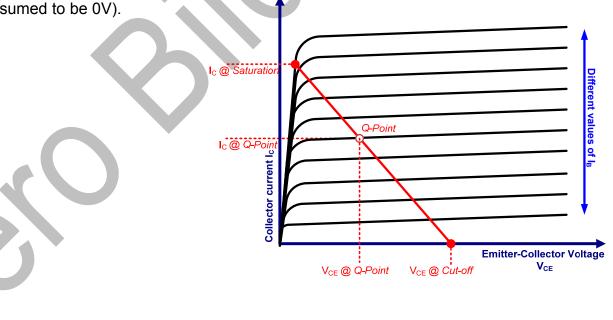

## Example:

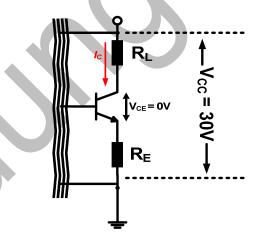

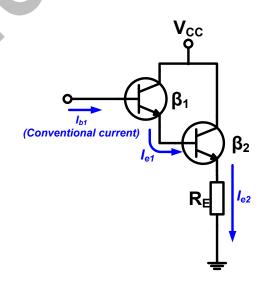

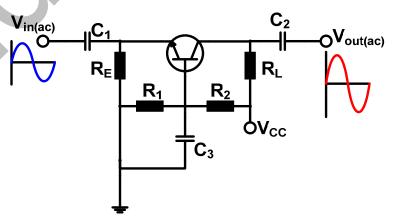

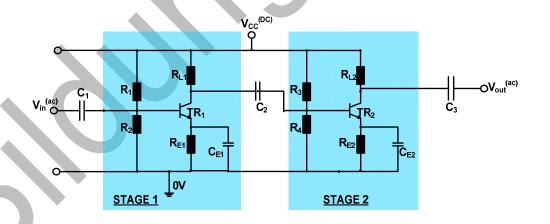

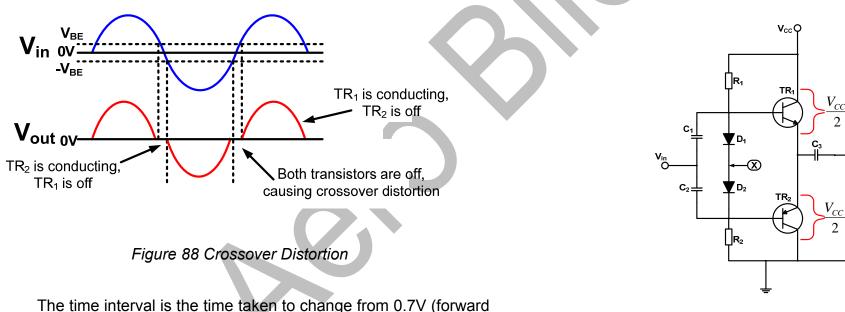

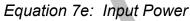

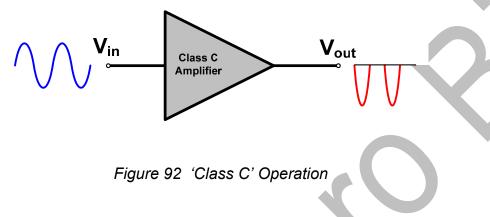

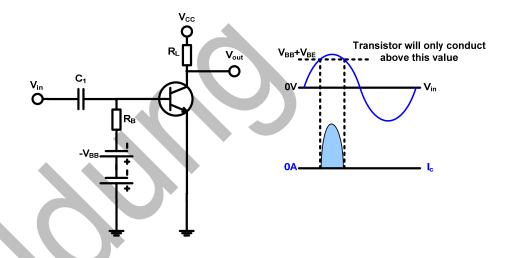

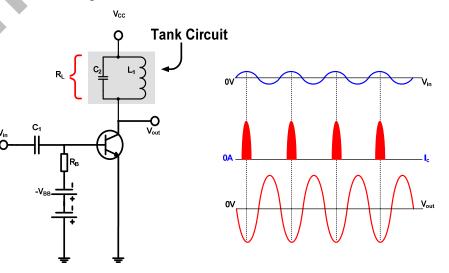

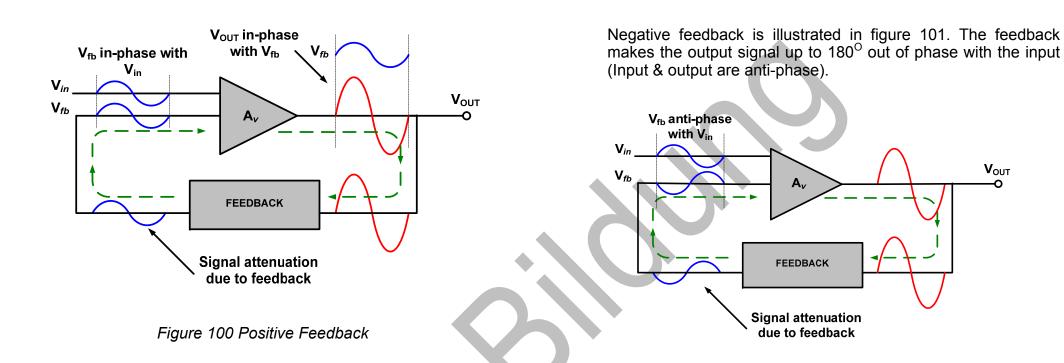

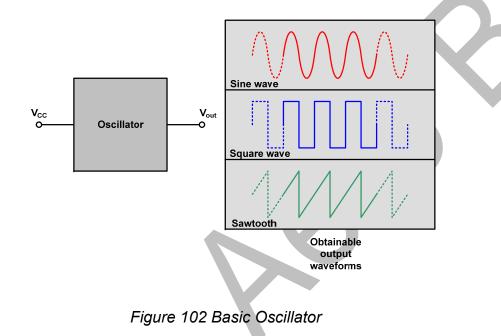

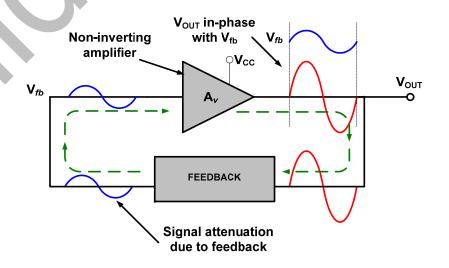

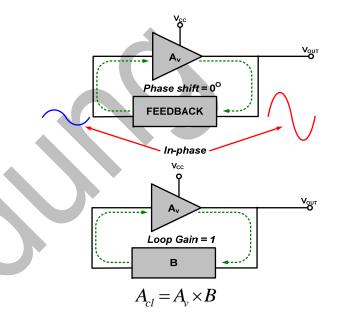

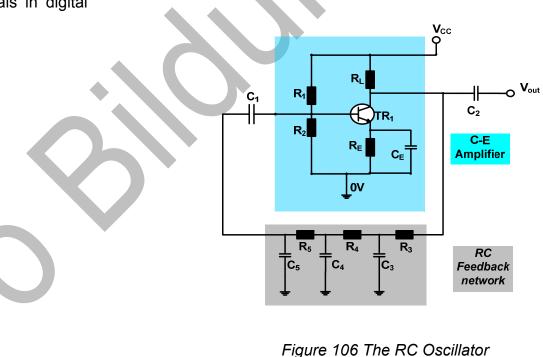

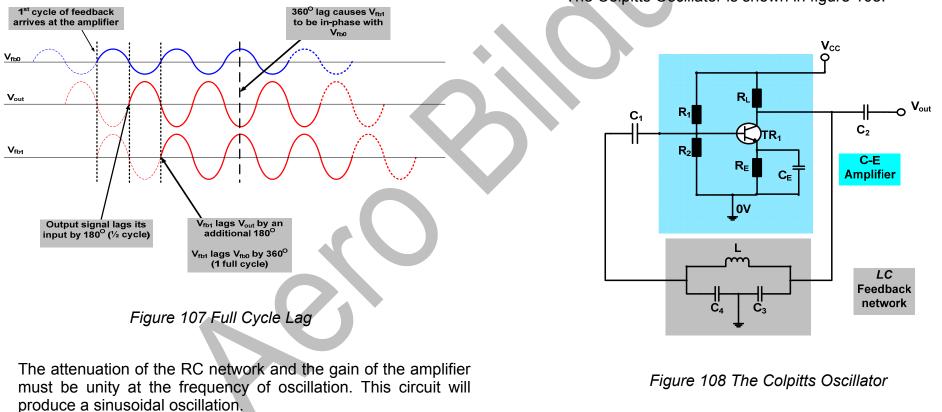

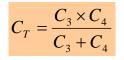

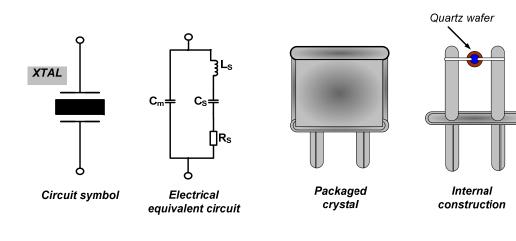

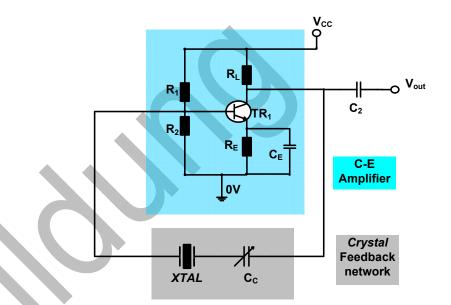

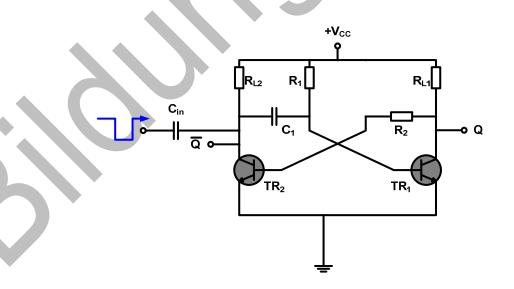

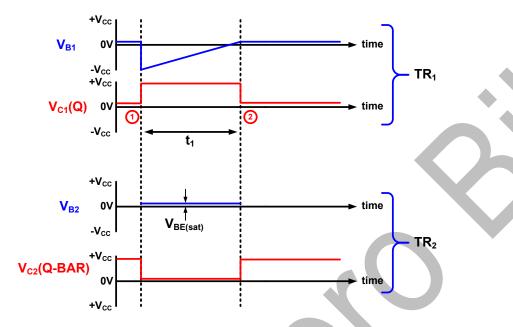

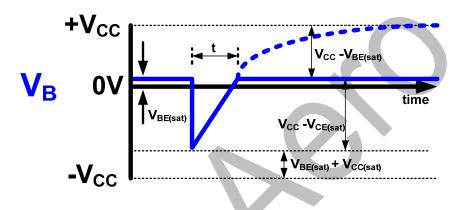

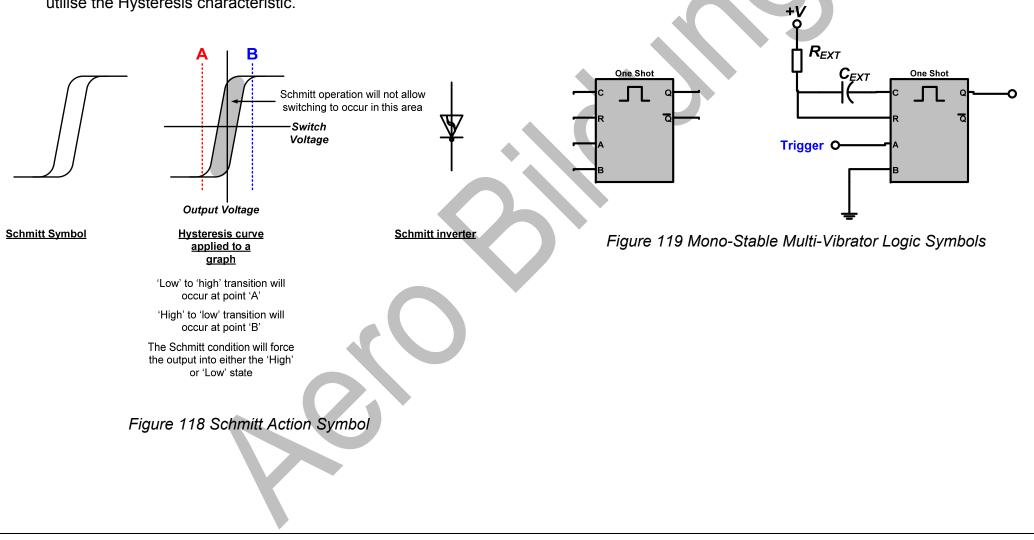

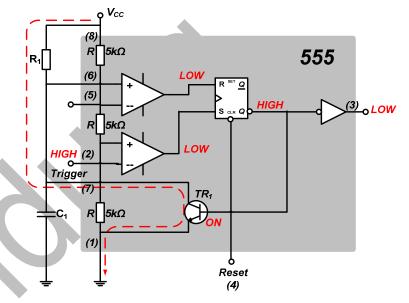

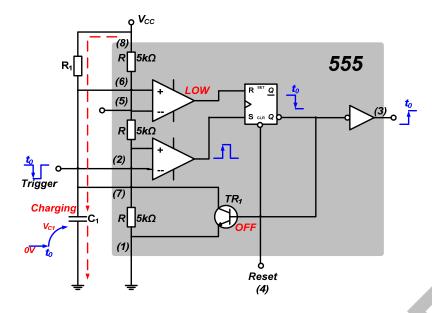

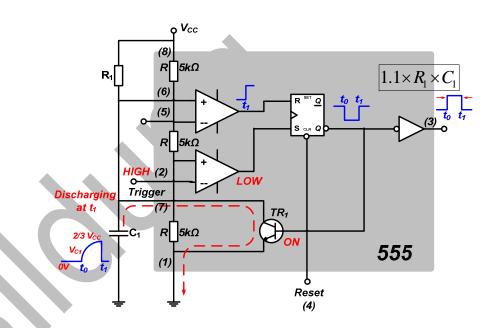

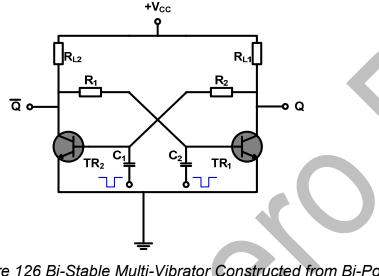

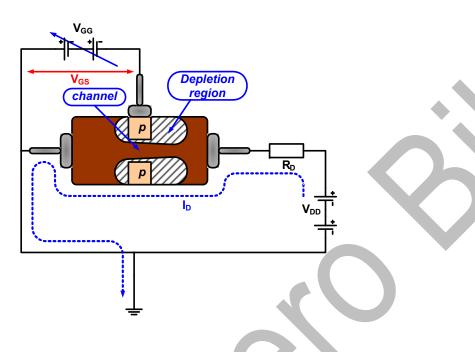

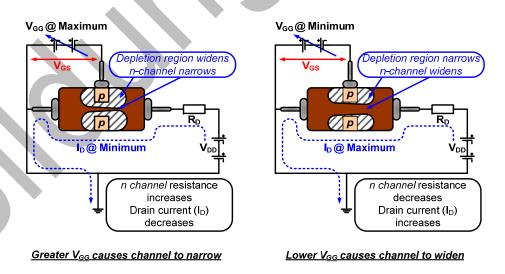

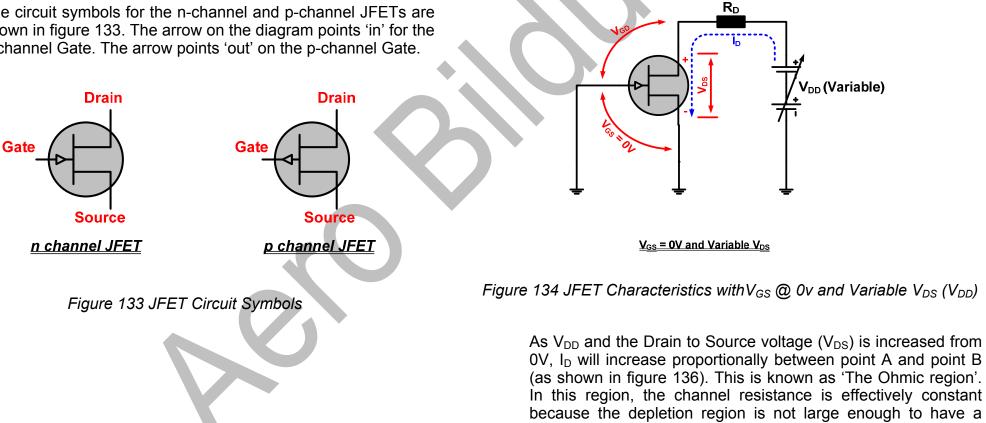

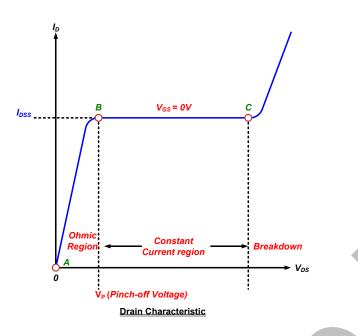

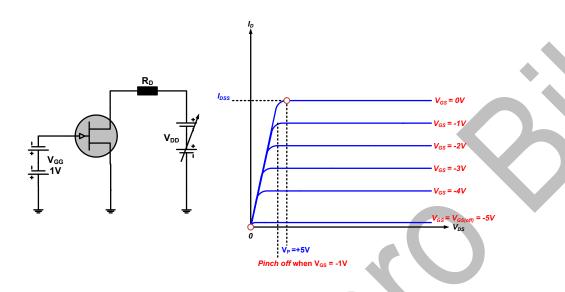

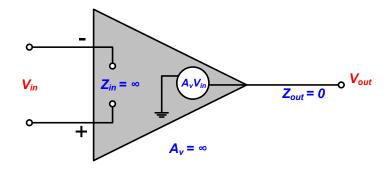

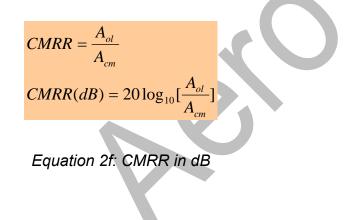

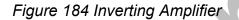

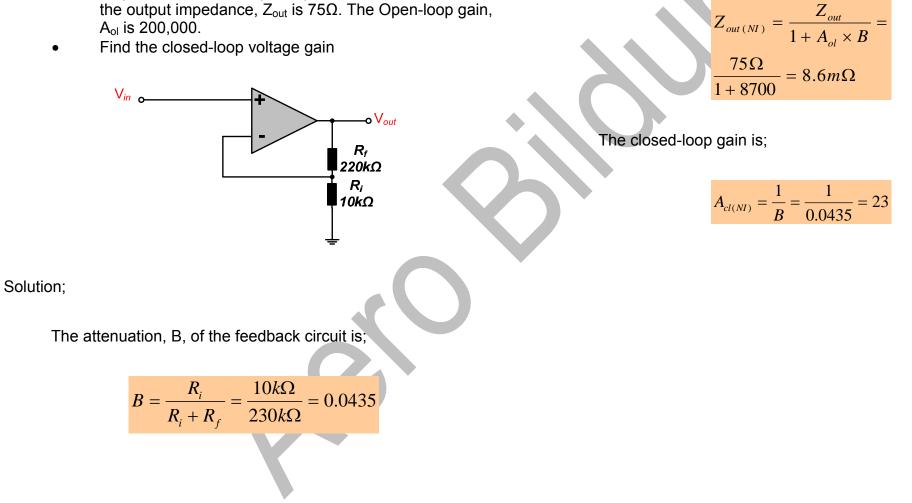

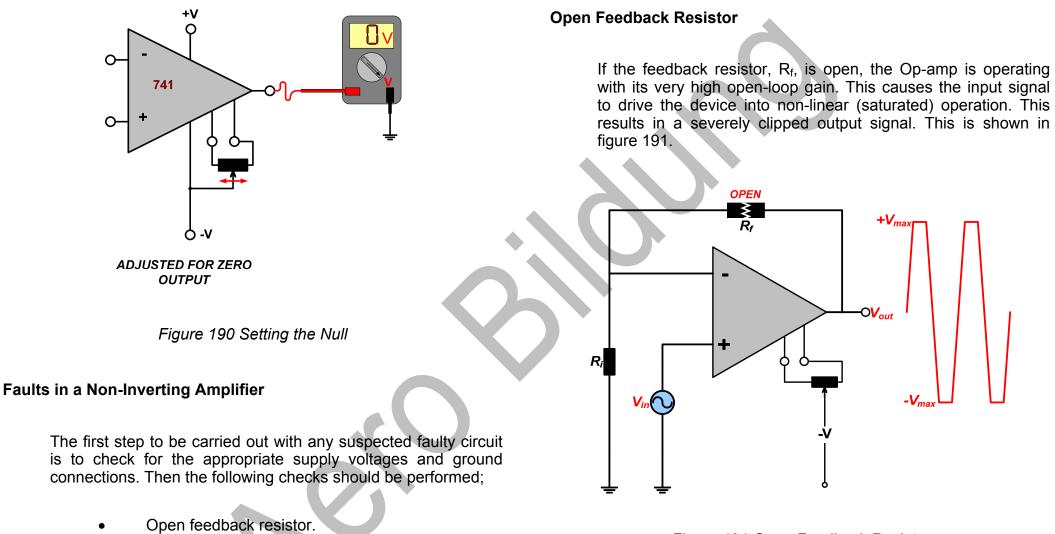

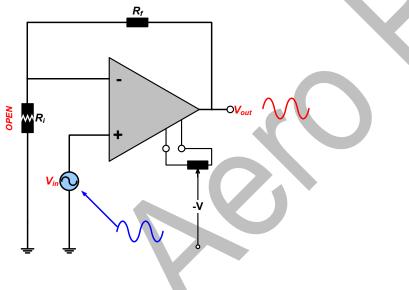

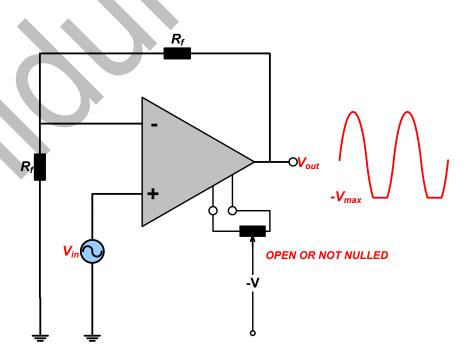

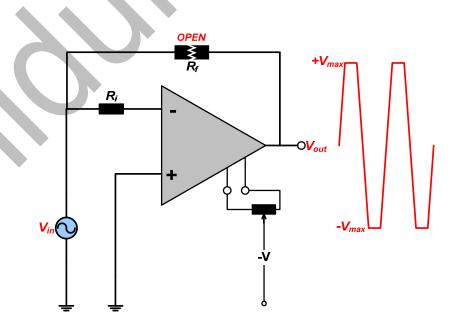

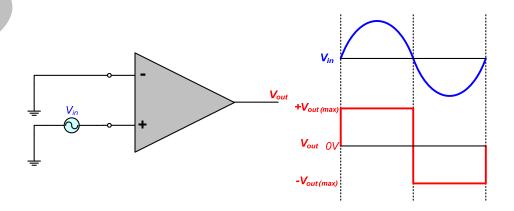

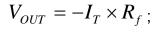

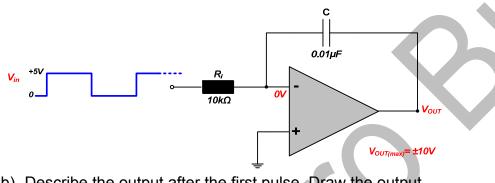

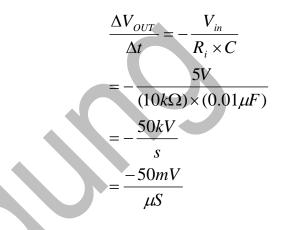

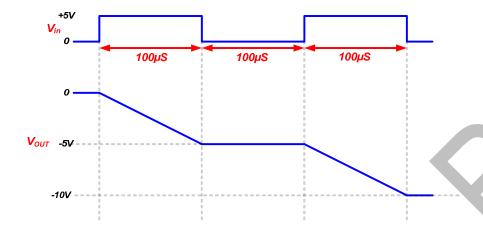

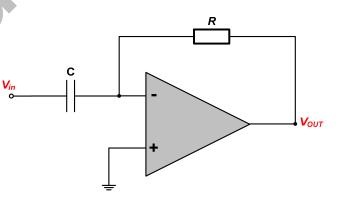

When the transistor operates in the Cut-off region, there is negligible Collector current (Assumed to be zero). This means that  $V_{CE}$  becomes the same value as the supply voltage ( $V_{CC}$ ). The term  $V_{CC}$  actually stands for Collector @ Cut-off (**Voltage Collector** at **Cut-off**). For this example,  $V_{CE}$  becomes 30V.